**Basic Research in Computer Science**

# Proceedings of the International Workshop on Software Tools for Technology Transfer STTT '98

Aalborg, Denmark, July 12–13, 1998

Tiziana Margaria Bernhard Steffen (editors)

**BRICS Notes Series**

NS-98-4 June 1998

BRIG

ISSN 0909-3206

Copyright © 1998, BRICS, Department of Computer Science University of Aarhus. All rights reserved.

> Reproduction of all or part of this work is permitted for educational or research use on condition that this copyright notice is included in any copy.

See back inner page for a list of recent BRICS Notes Series publications. Copies may be obtained by contacting:

> BRICS Department of Computer Science University of Aarhus Ny Munkegade, building 540 DK–8000 Aarhus C Denmark Telephone: +45 8942 3360 Telefax: +45 8942 3255 Internet: BRICS@brics.dk

**BRICS** publications are in general accessible through the World Wide Web and anonymous FTP through these URLs:

http://www.brics.dk

ftp://ftp.brics.dk

This document in subdirectory NS/98/4/

### STTT'98 International Workshop on Software Tools for Technology Transfer

Organizers

Volker Braun, University of Dortmund (D) W. Rance Cleaveland, NC State University (USA) Tiziana Margaria, University of Passau (D) Bernhard Steffen, University of Dortmund (D), (Chair)

### Preface

This volume contains the proceedings of the International Workshop on Software Tools for Technology Transfer, STTT'98, which took place in Aalborg (Denmark) on July 12–13 1998, as a satellite of ICALP'98, the 25<sup>th</sup> International Colloquium on Automata, Languages, and Programming.

Tool support for the development of reliable and correct computer systems is in fact of growing importance: a wealth of design methodologies, algorithms, and associated tools have been developed in different areas of computer science. However, each area has its own culture and terminology, preventing researchers from taking advantage of the results obtained by colleagues in other fields: tool builders often are unaware of, and thus unable to use, work done by others. The situation is even more critical when considering the transfer of technology into industrial practice.

STTT'98 addressed this situation by providing a forum for discussion of all aspects of tools that aid in the development of computer systems in the light of a possible tool-oriented link between academic research and industrial practice. Accordingly, the event comprised

- a **one-day Workshop**, on *July 12th*, whose eight talks were organized in three sessions:

- Verification of Code Generation: compiler-specific and programspecific verification.

- Model Checking: variants, also comprising real time aspects.

- Technology Transfer: initiatives and projects.

- a two-days Tool Exhibition, on *July 12th and 13rd*, which, in addition to the tools presented at the workshop, comprised a demonstration of the three tools described at the end of the proceedings.

We want to thank the local organization team for handling all the practical matters concerning the workshop, and in particular Josva Kleist who took care of all the technical frame conditions required for the demonstrations. Warm thanks are due also to Uffe Engberg for making the realization of this volume possible in record time, and to Claudia Herbers for her assistance in the coordination of the review process.

July 1998

Tiziana Margaria Bernhard Steffen

### Contents

### **Regular Sessions**

### **Tool Exhibition**

| C-Mix: Making Easily Maintainable C-Programs run FAST |   |

|-------------------------------------------------------|---|

| The C-Mix Group                                       | 1 |

| Rapid Prototyping with APICES                         |   |

| Ansgar Bredenfeld                                     | 7 |

| Performance Evaluation Methodology-and-Tool for Computer |    |

|----------------------------------------------------------|----|

| Systems with Migrating Applied Software                  |    |

| S.L. Frenkel                                             | 83 |

#### The Code Validation Tool (CVT)-

#### Automatic verification of code generated from synchronous languages<sup>®</sup>

A. Pnueli, O. Shtrichman and M. Siegel

Contact author: amir@wisdom.weizmann.ac.il

The Weizmann Institute of Science, Department of Applied Mathematics and Computer Science Rehovot, Israel

#### Abstract

We describe CVT - a fully automatic tool for Code-Validation, i.e. verifying that the target code produced by a code-generator (equivalently, a compiler or a translator) is a correct implementation of the source specification. This approach is a viable alternative to a full formal verification of the code-generator program, and has the advantage of not 'freezing' the code generator design after verification.

The CVT tool has been developed in the context of the ESPRIT project SACRES, and validates the translation from StateMate/Sildex mixed specification into C. The use of novel techniques based on uninterpreted functions and their analysis over a BDD-represented small model enables us to validate source specifications of several thousands lines, which represents a typical industrial size safety-critical application.

#### 1 Introduction

A significant number of embedded systems contain safety-critical aspects. There is an increasing industrial awareness of the fact that the application of formal specification languages and their corresponding verification/validation techniques may significantly reduce the risk of design errors in the development of such systems. However, if the validation efforts are focused on the specification level, the question arises how can we ensure that the quality and integrity achieved at the specification level is safely transferred to the implementation level. Today's process of the development of such systems consists of hand-coding followed by extensive unit and integration-testing.

The highly desirable alternative -- both from a safety and a productivity point of view -- to automatically generate code from verified/validated specifications, has failed in the past due to the lack of technology which could convincingly demonstrate to certification authorities the correctness of the generated code. Although there are many examples of compiler verification in the literature (See, for-example, [1][2][3] and [4]), the formal verification of industrial code-generators is generally prohibitive due to their size. Another problem with compiler verification is that the formal verification freezes their designs, as each change to the code generators nullifies their previous correctness proof.

Alternately, code-validation suggests to construct a fully automatic tool which establishes the correctness of the generated code individually for each run of the code generator. In general, code-validation is the key enabling technology to allow the usage of code generators in the development cycle of safety-critical and high quality systems. Remarkably, the combination of automatic code generation and validation improves the design flow of embedded systems in both safety and productivity by eliminating the need for hand-coding of the target code (and consequently coding-errors are less probable) and by considerably reducing unit/integration test efforts.

The work carried out in the SACRES project proves the feasibility of code-validation for the industrial code generators used in the project, and demonstrates that industrial-size programs can be verified fully automatically in a reasonable amount of time. In the next section we describe the SACRES project and the role of code validation in this context. In section 3 we briefly describe the logical basis of the correctness proof. In section 4 we describe the architecture of CVT and the role of each of its modules, and we summarize in section 5 by presenting preliminary results from an industrial case study that we are currently working on.

<sup>&</sup>lt;sup>\*</sup> This research was done as part of the ESPRIT project SACRES, and was supported in part by a grant from the Deutsche Forschungs Gemeinschaft, the Minerva Foundation, and an infra-structure grant from the Israeli Ministry of Science and Art.

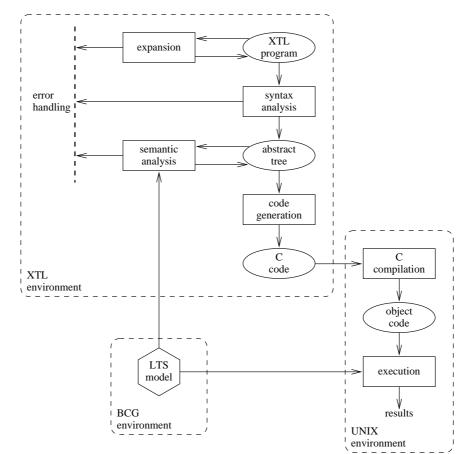

#### 2 Code validation in the context of the SACRES project

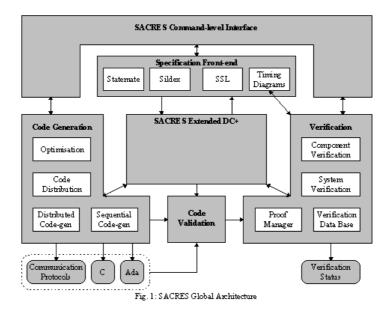

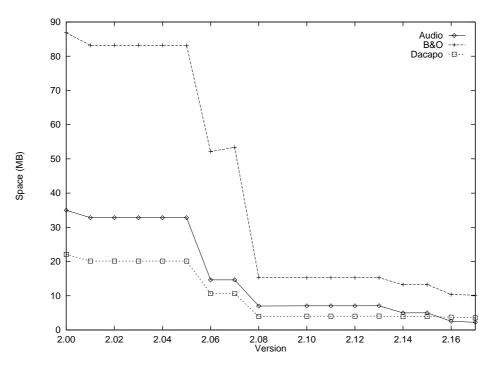

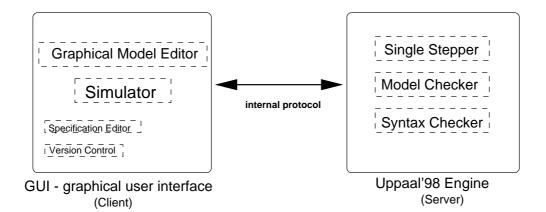

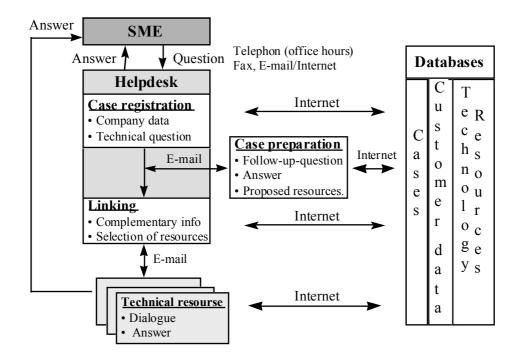

The Code Validation Tool (CVT) is developed as part of the ESPRIT-supported project SACRES (which stands for *Safety Critical Real-time Embedded Systems*)[7]. The objective of this project is to provide designers of safety-critical systems with an enhanced design methodology supported by a toolset, significantly reducing the risk of design errors and shortening the overall design time. The emphasis within the project is on formal development of systems, providing formal specification, model checking technology and validated code-generation. The architecture of the SACRES toolset is shown in Figure 1.

Following is a typical scenario of usage of the toolset: After completing the design in her favorite design tool (currently the 'StateMate' and 'Sildex' tools are supported), the user invokes the automatic translation of designs into DC+, the common format for synchronous languages. The design can be mixed: different components can be designed in different tools, as long as these tools are supported in the toolset. In the next step the user invokes the *Proof-Manager*, and performs *component and system verification*. In this stage the user verifies that the design satisfies various properties, which she expresses in the requirement specification language of *Timing Diagrams*, using the *Timing-Diagrams Editor (TDE)*. These properties typically correspond to the requirements listed in a requirement document, or to general safety and liveness properties of the system, such as the absence of deadlocks.

The Proof-Manager combines BDD-based automatic verification tool and a theorem-prover, which is invoked when the automatic verification fails (typically due to the size of the model). The various components thus can be verified by different means, while the proof-manager guarantees that the necessary compositionality requirements are maintained. If the system finds a design error, it presents a counter example by means of simulation (either in StateMate or in TDE).

After the design is verified, the user invokes the code generator (produced by the SACRES partner TNI) to automatically generate executable code (C or ADA). This is where the code validation tool is invoked: The validation of the generated code via CVT establishes that the code generator worked as expected and thus the properties which were verified at the specification level are preserved at the implementation level. We expect that the process of code validation will provide the convincing evidence required by the certification authorities in order to allow the use of automatic code generators for the development of safety-critical systems.

#### 3 The Verification Condition

The theoretical background behind the construction of the verification condition is elaborated in [5]. Following is a brief description of the structure of the verification condition, which, if proven correct, guarantees the correctness of the translation.

In the following, we refer to the DC+ program as the *abstract* system, as it represents the specification, and to the C program as the *concrete* system, as it represents the concrete implementation. We denote the variables, initial condition and transition relation of these systems by  $V_A$ ,  $\theta_A$  and  $\rho_A$  (abstract) and  $V_C$ ,  $\theta_C$  and  $\rho_C$  (concrete), respectively. In order to establish that the concrete system correctly implements (*refines*) the abstract system, we use two premises (verification conditions), **R1** – the *base case*, and **R2** – the *induction step*.

The base case requires that  $\theta_C$  implies  $\theta_A$ , after performing an appropriate substitution  $\alpha$  of each (observable) variable  $v \in V_A$  by an expression  $\varepsilon$  over  $V_C$ . Such a substitution induces an (abstraction) mapping between the states of the two systems.

The induction step requires that  $\rho_C$  implies  $\rho_A$ , once again, after an appropriate substitution  $\alpha$ . Taken all together, the refinement rule has the following structure:

| Let $\alpha: V_A \rightarrow \varepsilon(V_c)$      | be a substitution  |

|-----------------------------------------------------|--------------------|

| <b>R1</b> : $\theta_c \rightarrow \theta_A[\alpha]$ | The base step      |

| <b>R2</b> : $\rho_c \rightarrow \rho_A[\alpha]$     | The induction step |

C imp A

The Verification Condition Generator, which is the first module invoked in CVT, generates these implications from the C and DC+ source codes.  $\rho_A$  and  $\rho_c$  are both large conjunctions of atomic sub-formulas, where typically (but not always) each sub-formula corresponds to an assignment line in the code or a constraint imposed by the abstraction (see section 4 for more details). These sub-formulas reflect the semantics of the source languages and the mapping between their variables.

#### 4 The CVT - Architecture

The code-validation package offers a fully automatic routine which establishes the correctness of the generated code individually for each run of the code generator. Therefore, there is no user-interface to this tool - just configuration parameters and a command line.

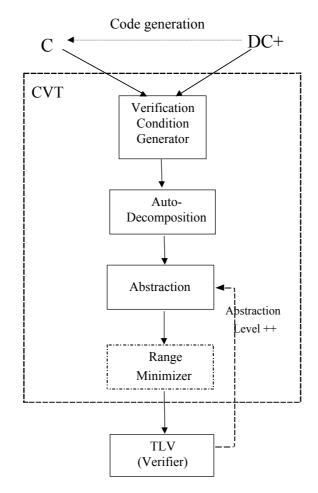

The overall architecture of CVT can be seen in Figure 2. We will not focus in this (short) paper on the underlying theory behind the verification condition. As mentioned before, a detailed explanation of this can be found in [5]. Rather we explain what is the role of each module and what are its inputs and outputs.

Fig. 2 : CVT Architecture (The 'Range Minimizer' module is not yet part of CVT)

#### 4.1 The Verification Condition Generator module

CVT receives as input the DC+ and C source codes. These are the source and target code for the code generator. Two separate sub-modules (appearing united in Figure 1 as the Verification Condition Generator module) generate the verification conditions (which are actually a large logical implication) by means of various translations and transformations. The validity of this logical implication implies the correctness of the generated code w.r.t. the source code while its invalidity indicates a potential mistake in the code generation process. Each of the conditions is separated into two files representing the left and right hand side of the implication (in **R2** these are  $\rho_c$  and  $\rho_A$ ). Since at the end of this process we use TLV [6] as a decision procedure, the verification condition is generated in the appropriate format (the models TLV expects are compatible with the more broadly used SMV model-checker).

#### 4.2 The Auto-Decomposition module

The next step is Auto-Decomposition. We are interested in handling industrial-size programs, and therefore decomposition is essential. As will be demonstrated in section 5, the auto-decomposition is one of the key enabling steps for scalability. The Auto-Decomposition module takes advantage of the fact that the right hand side of the premises are in the form of a conjunction (typically of hundreds of expressions), and simply breaks it into smaller conjuncts which can be verified independently.

The size of the decomposed conjuncts is set by a configuration parameter (called the 'chunk size'), and can range from 1 (a single conjunct) to the total number of conjuncts. In the later case the entire formula will be verified at once, which is only possible for relatively small files. After breaking the right hand side, the Auto-Decomposition module returns to the left hand side of the implication, and calculates the *cone of influence*, i.e. the portion of the formula in the left hand side that is needed for proving the selected conjuncts on the right-hand side. After repeating this process until all conjuncts are covered, we are left with (possibly hundreds) pairs of files, each significantly smaller than the original ones. There is an obvious tradeoff between having files with very small right hand side, which leads to significantly shorter verification time, and the number of these files which incurs an additional invocation overhead cost associated with each file. It is therefore left to the user to decide on the chunk size which may be optimal for her case.

Another configuration option in the Auto-Decomposition module is called 'back calculation'. When this flag is set, after calculating the cone of influence, the program returns to the right hand side and looks for additional conjuncts that can be proven with the same cone that was just calculated. This option is useful for reducing the number of files and reducing the over-all time for performing the proof (the time TLV takes mainly depends on the transition relation of the model, i.e. the left hand side. Thus if we use the same model for proving more conjuncts, we save time). When setting this option, the 'chunk size' is no longer an exact number of conjuncts taken each time, rather it is the size of the initial set of conjuncts, which possibly grows after the back calculation. The efficiency of the back calculation obviously depends on the ordering of conjuncts we are investigating. An optimal ordering would be such that if  $cone(C_i) \subseteq cone(C_j)$  then  $C_i$  and  $C_j$  are verified together (with simple sequential ordering this will happen only if  $C_j$  appears first or if  $cone(C_i) = cone(C_j)$ ). This ordering can be achieved, for example, by calculating all the cones and then partitioning the files accordingly. We did not implement this because we suspect that the overhead of this calculation will be larger than the saving resulting from the better ordering.

#### 4.3 The Abstraction Module and the Range-Minimizer module

After decomposing the files, CVT invokes the Abstraction module. Once again, the underlying theory of the abstraction is detailed in [5]. Basically, abstraction is needed since we are trying to verify a model which contains integer and float variables, as well as functions over these variables using a BDD-Based decision procedure for finite-state models. The abstraction module treats these functions as *uninterpreted functions*, replacing them by new symbols. The faithfulness of this technique depends on the way that the compiler manipulates these functions and the kind of functions we leave interpreted. The more we interpret, the more faithful the model is. On the other hand, the less we interpret, the smaller the model is.

The abstraction module works in an incremental manner, following an *abstraction hierarchy* designed according to the specific optimizations the compiler performs. We begin with maximum abstraction (called *Level-0 abstraction*) where all functions except equalities, Boolean operators and if-then-else are uninterpreted. If the proof fails, CVT invokes the abstraction module again, asking for *Level-1 abstraction*, where additionally comparisons operators on integers ('>', '<', etc) are left interpreted.

If, for example, the compiler reads 'a < b' in the abstract system and transforms it to 'b > a' in the concrete system (which are obviously semantically equivalent), Level-0 abstraction will result in a false negative where as level-1 will succeed.

The reason we first interpreted the comparison operators on moving from level-0 to level-1 is that the compiler we are considering employs these kinds of optimizations frequently. To handle comutativity of the '+' function, for

example, we need another abstraction level. However, so-far Level-0 and Level-1 abstractions proved to be sufficient for the purposes of code-validation of the examples we have considered.

After we replace the appropriate terms by new variables, we impose additional constraints on the verification conditions to ensure functionality. This leaves us with a quantifier-free first-order logic formula which enjoys the small model property (i.e. it is satisfiable iff it is satisfiable over a finite domain). Therefore the next issue the abstraction module handles is the calculation of a finite domain, such that the formula is valid iff it is valid over all interpretations into these domains. The latter can be checked algorithmically, using BDD techniques. The domain that is currently taken is simply a finite set of integers whose size is the number of (originally) integer/float variables, although smaller domains can be achieved by analyzing the structure of the formula considered. This analysis is performed by the 'Range Minimizer' module, not yet implemented, which we expect to significantly reduce the range of each of these (now enumerated type) variables, and thus increase the size of programs we can handle. Preliminary results from this approach show that most models can be verified by using a state-space which is orders of magnitude smaller than the state-space resulting from using our current method.

#### 4.4 The Verifier module (TLV)

The validity of the verification conditions is checked in TLV [6], an SMV-based tool which provides the capability of BDD-programming and has been developed mainly for finite-state deductive proofs (and thus convenient in our case for expressing the refinement rule). In the case that the equivalence proof fails, a counter example is displayed. Since it is possible to isolate the conjunct(s) that failed the proof, this information can be used by the compiler developer to check what went wrong. CVT invokes TLV for each pair of files generated by the Auto-Composition module. A proof log is generated as part of this process, indicating which files were proved, at what level of abstraction and when.

#### 5 A case study

Currently we are working on the validation of an industrial size program, a code generated for the case study of a turbine developed by SNECMA, which is one of the industrial case studies in the SACRES project. The program was partitioned manually (by SNECMA) into 5 units which were separately compiled. Altogether the DC+ specification is a few thousand lines long and contains more than 1000 variables. After the abstraction we had about 2000 variables (as explained in subsection 4.3, the abstraction module replaces function symbols with new variables). Following is a summary of the results achieved so far:

| Module  | Conjuncts | Verified | Time (min.) |

|---------|-----------|----------|-------------|

| M1      | 530       | 100%     | 4:14        |

| M2      | 533       | 100%     | 1:30        |

| M3      | 124       | 92%      | ?           |

| M4      | 308       | 99.3%    | 3:32 + ?    |

| M5      | 860       | 80%      | ?           |

|         | 2255      | 02.00/   | 0.1( + 0    |

| Total : | 2355      | 93.9%    | 9:16 + ?    |

As can be seen, about 6.1% of the conjuncts in our case could not be verified in reasonable time using the current implementation of CVT. We hope that after installing the Range-Minimizer this problem will be solved.

#### References

- [1] B. Buth, K. Buth, M. Franzle, B. Karger, Y. Lakhneche, H. Langmaack, and M. Muller-Olm. Provably correct compiler development and implementation. In *Compiler Construction* '92, 1992.

- [2] D.L. clutterbuck and B.A. Carre. The verification of low-level code. *Software Engineering Journal*, pages 97-111, 1998.

- [3] P. Curzon. A verified compiler for a structured assembly language. In *proceedings of the 1991 international* workshop on the HOL theorem Proving System and its applications. IEEE Computer Society Press, 1992.

- [4] I. M. O'Neill, D. L. Clutterbuck, P.F. Farrow. The formal verification of safety-critical assembly code. In proceedings of the IFAC Symposium on safety of computer control systems 1988.

- [5] A. Pnueli, O. Shtrichman and M. Siegel. Translation Validation for Synchronous Languages. To appear in *ICALP*' 98.

- [6] A. Pnueli and E. Shahar, A Platform for Combining Deductive with Algorithmic Verification. 8th Conference on Computer Aided Verification, Springer-Verlag, 1996

- [7] The SACRES web page: http://www.ilogix.co.uk/ilogix/technica.html

#### Mechanized Verification of Compiler Backends

Axel Dold<sup>1</sup>, Thilo Gaul<sup>2</sup>, and Wolf Zimmermann<sup>2</sup>

<sup>1</sup> University of Ulm, Oberer Eselsberg, D-89069 Ulm, {dold}@ki.informatik.uni-ulm.de

<sup>2</sup> University of Karlsruhe, Zirkel 2, D-76131 Karlsruhe, {gaul;zimmer}@ipd.info.uni-karlsruhe.de

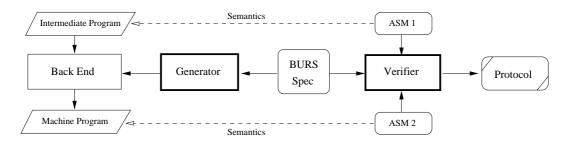

Abstract We describe an approach to mechanically prove the correctness of BURS specifications and show how such a tool can be connected with BURS based back-end generators [9]. The proofs are based on the operational semantics of both source and target system languages specified by means of Abstract State Machines [15]. In [31] we decomposed the correctness condition based on these operational semantics into local correctness conditions for each BURS rule and showed that these local correctness conditions can be proven independently. The specification and verification system PVS is used to mechanically verify BURS-rules based on formal representations of the languages involved. In particular, we have defined PVS proof strategies which enable an automatic verification of the rules. Using PVS, several erroneous rules have been found. Moreover, from failed proof attempts we were able to correct them.

#### 1 Introduction

There exist a variety of techniques to construct efficient code producing compiler back-ends with sufficient tool support. There do also exist approaches on the construction of verified code generators but they do not fulfill at least one of the following requirements that are essential to the code generation part of pratical compiler environments: (i) compilation to native machine code, (ii) ability to deal with complex real-life programming languages, (iii) to produce efficient machine code, comparable to non-verified compilers and (iv) tool support for the compiler writer.

Usually the correctness proofs of programs or program derivations assume that the programs are written in higher-level languages. However, the program is compiled into binary code and it is this code, that is executed. Therefore the correctness of programs depends also on the correctness of the compiler which compiles the higher-level language into the machine language of the processor, and on the correctness of the processor. This paper discusses aspects for the construction of realistic correct compilers.

Realistic correct compilers should produce machine code whose performance is comparable to machine code produced by usual compilers. Practical experiences show that the main performance gains and losses result from the back-end of compilers. Therefore, we focus on the construction of correct compiler back-ends. Compiler back-ends transform low-level intermediate language programs into machine programs.

One of the well known techniques to produce efficient machine code are bottom up rewrite systems (BURS). This specification technique [9, 10, 22, 23, 27] has two advantages: (i) the back-end can be generated from such a specification, (ii) it is possible to specify back-ends which produce efficient code.

We show in this paper how rewrite rules for code generation can be pratically proven correct, thus the BURS technology becomes applicable to the construction of verified compilers.

In [31] we decomposed the correctness of BURS-based compiler back-ends into the local correctness of single term-rewrite rules, and the global correctness. Furthermore we proved the global correctness under the same constraints as the applicability of the BURS-technology, i.e. no specific assumptions on the term-rewrite system are required. In this paper we put the main stress on the local correctness of single rewrite rules.

In practice BURS specifications have a large number of TRS rules. Therefore a mechanical verification of the local correctness is necessary. This paper shows proof strategies sufficient to prove local correctness of TRS rules and its mechanization using PVS [24]. Our approach is to give operational semantic specifications for source and target language, and to prove the correctness of single transformations by symbolic execution of the program pieces. The semantic and transformation rule specifications have been formalized into PVS. Together with PVS proof strategies we are able to automatically verify the rules. Using these strategies, errorneous rules have been found, and, moreover, from failed proof attempts these errors could be corrected by a careful inspection of the proof strate.

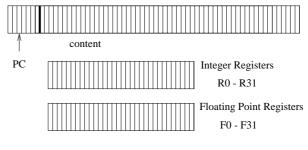

We demonstrate our approach with a typical basic block oriented intermediate language with expressions (**MIS**) and the translation to the DEC-Alpha processor family. The operational semantics is formalized by abstract state machines (Section 2). In this paper, the mapping of composite datatypes such as records, arrays etc. is considered as a front-end task.

The first work on correct compilers is [17]. Most of the following work on correct compilation is based on denotational semantics (e.g.[4, 18, 19, 25, 26, 30]) or on refinement calculi (e.g.[5, 6, 16, 20, 21]). Other work on compiler correctness based on refinement use abstract state machine (e.g.[1–3]). Most of these works do not compile high-level programming languages into assembler languages. To our knowledge, only [2, 3, 20, 21] and ProCos [16] discus transformations into machine code. The performance of code generated by semantics driven code generation is poor and by one or more orders of magnitude slower than the code generated by compilers used in practice [25]. [2, 3, 20, 21] consider the compilation into transputer code. We compare our measerument results with those from [7]. To our knowledge the only work on "correct compilers" which provides performance measurements.

This article is organized as follows: First we give the basic definitions of abstract state machines and correctness notion in Section 2.

Our definition of BURS specifications (Section 3) define the local correctness conditions and central theorem of [31]. Section 4 gives the general proof strategy for proving local correctness and demonstrates it by some examples. Section 5 describes the formalization of the intermediate and target language ASM's, the formal representation of the TRS rules and their verification using proof strategies. In particular, the detection and correction of an erroneous rule using PVS is presented.

#### 2 Basic Definitions

The semantics of our languages are defined operationally by abstract state machines [14]. The notation is oriented on [15], and can be found in following subsection.

In Appendix A we define a typical intermediate language with expressions (**MIS**), which is based on basic block graphs (see e.g. [29]). Our example target language is the machine language of the DEC-Alpha processor family (Appendix B). The complete definitions can be found in [12] and [13].

#### 2.1 Abstract State Machines

An abstract state machine is a tuple  $\mathcal{A} = (\Sigma, Q, S, \rightarrow, I)$ , where

- (i)  $\Sigma$  is a signature, i.e. a finite collection of function names, each of a fixed arity.

- (ii) the set of states Q is a set of  $\Sigma$ -algebras,

- (iii) a superuniverse S representing the sorts,

- (iv)  $\rightarrow \subset Q \times Q$  is the transition relation, and

- (v)  $I \subset Q$  is the set of *initial states*.

$f_q$  denotes the interpretation of  $f \in \Sigma$  in state  $q \in Q$ . Interpretations on S of function names in  $\Sigma$  are called *basic functions*. The superuniverse does not change when the state of  $\mathcal{A}$  changes, the basic functions may. The superuniverse contains distinct elements *true*, *false* and *undef* ( $\perp$ ) that allow to deal with binary relations and partial functions. They do not appear in the signature.

A universe U is a special type of basic function: a unary relation identified with the set  $\{x : U(x)\}$ . Any sort  $U \in S$  denotes a universe. The universe BOOL is defined as  $BOOL = \{true, false\}$ . A function  $f : U \to V$  from an universe U to an universe V is an unary operation on the superuniverse such that  $f(a) \in V$  for all  $a \in U$  and  $f(a) = \bot$  otherwise. The type INT is also used to denote the 64-bit integer arithmetic of the DEC-Alpha Processor. INT[k] denotes the integer represented by k Bits, i.e. the range  $-2^k, \ldots, 2^k - 1$ . Floating point types are not used in this article.

A term over the signatur  $\Sigma$  is defined as usual.  $\mathcal{T}(\Sigma)$  denotes the set of terms over the signature  $\Sigma$ . The interpretation of a term  $t \in \mathcal{T}(\Sigma)$  in state q is denoted by  $[t]_q$ . Sometimes we need a set of variables V.  $\mathcal{T}(\Sigma, V)$  denotes the set of term over signatur  $\Sigma$  and variables V. As usual,  $\stackrel{*}{\rightarrow}$  denotes the reflexive, transitive closure and  $\stackrel{+}{\rightarrow}$  denotes the transitive closure of  $\rightarrow$ . A state  $q \in Q$  is *reachable* iff there is an initial state  $i \in I$  such that  $i \stackrel{*}{\rightarrow} q$ . The relation  $\rightarrow$  is defined by a finite collection of transition rules of the form:

if Condition then Updates endif

For example

if  $t_0$  then  $f(t_1, ..., t_n) := t_{n+1}$  endif

where  $t_0, t_1, \ldots, t_{n+1} \in \mathcal{T}(\Sigma)$  is a transition rule. Let q be a state before and q' be a state after applying the rule. The meaning of the rule is: If  $\llbracket t_0 \rrbracket_q = true$  then for all  $g \in \Sigma \setminus f g_{q'} = g_q$ , and  $f_{q'}$  is defined as follows:

$$f_{q'}(x_1,\ldots,x_n) = \begin{cases} \llbracket t_{n+1} \rrbracket_q & \text{if for all } i, \ 1 \le i \le n, \ \llbracket t_i \rrbracket_q = x_i \\ f_q(x_1,\ldots,x_n) & \text{otherwise} \end{cases}$$

If  $[t_0]_q = false$  then  $f_q = f_{q'}$  for any  $f \in \Sigma$ . Thus the interpretation changes the value of the basic function f at the value of the tuple  $(t_1, \ldots, t_n)$  to the value  $t_{n+1}$ , provided that  $[t_0]_q = true$ . If several updates contradict then one update is chosen nondeterministically. We distinguish the following classes of functions:

- dynamic functions: the interpretation of a dynamic function is changed by transition rules, i.e. f is called a dynamic function if an assignment of the form  $f(t_1, \ldots, t_n) := t_{n+1}$  appears anywhere in a transition rule.

- static functions: the interpretation of a static function is never changed by a transition rule.

*Macros* are abbreviations and denoted by  $macro \doteq expr$ . Whenever macro is used, it is replaced by expr. We assume that macro definitions define a noetherian and confluent rewrite system.

#### 2.2 Correctness Notion

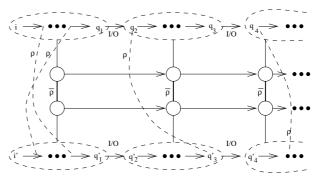

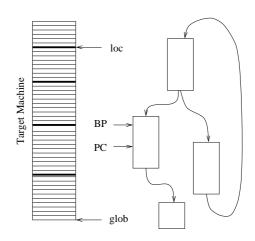

The definition of compiler correctness is based on the operational semantics of the source and target languages, respectively. An operational semantics for a language L defines a family of abstract state machines  $\mathcal{A}_{\pi}$  for every program  $\pi \in L$ . The state transitions are based on the instruction set of L (cf. Appendix A). Not all state transitions are relevant. State transitions that correspond to jumps, memory access, procedure calls etc. must be distinguished from state transitions that read an input and write an output. The former are not observable while the latter are observable. We therefore distinguish observable behaviour. Formally, a behaviour of program  $\pi$  is a set of finite or infinite sequences of states  $q_0 \rightarrow q_1 \rightarrow \cdots \rightarrow q_n$ , where  $q_i \rightarrow q_{i+1}$  is the transition from state  $q_i$  into state  $q_{i+1}$  by the ASM of the program. The observable behaviour focuses on the input/output. Figure 1 illustrates the observable

behaviour by merging all states where the following state transition does not change input or output. [31] defines these definitions formally.

A compiler which compiles a program  $\pi_1 \in L_1$  into a program  $\pi_2 \in L_2$  implements a relation  $\mathcal{C} : L_1 \times L_2$ . Intuitively,  $\mathcal{C}$  is correct if  $\pi_1$  and  $\pi_2$  have the same observable behavior. We base the correctness definition on simulations, i.e.  $\mathcal{A}_{\pi_2}$  simulates  $\mathcal{A}_{\pi_1}$  in a sense similar to the notion of simulations used in complexity and computability theory. Figure 1 illustrates these ideas. Full definitions can be found in [31].

The relation  $\bar{\rho}$  maps injectively the observable part of the states of the target program to the observable part of the states of the source program. For every observable behaviour of the target program, there must be a corresponding observable behaviour of the source program.  $\bar{\rho}$  can be implemented by a relation  $\rho$  which is compatible with  $\bar{\rho}$ , i.e., any states can be related by  $\rho$  whose observable part is related by  $\bar{\rho}$ .  $\rho$  is usually implemented by a compiler. The freedom of choice of  $\rho$  allows optimizations. In particular, the order of instructions can be changed as long as the observable behaviour is preserved.

Figure1. Compiler Correctness

#### 2.3 Code Generation by Term Rewriting

Term rewriting is commonly used in compiler back-end generators for the specification of the transformation to be performed by the code selection, i.e. the mapping  $CS : IL \Rightarrow IL'$ . Any intermediate language command can be viewed as a term. The basic idea is to reduce this term to a constant and to generate code for each applied reduction step. The sub-class of rewrite systems used in this article are the Bottom-Up-Rewrite-Systems, the commonly used technique for code generators.

A term-rewrite rule  $t \Rightarrow X$ ;  $\{m_1, \ldots, m_n\}$  specifies a compilation in the sense that sequence  $m_1, \ldots, m_n$  is the sequence of machine instructions that implement t. The machine instructions  $m_1, \ldots, m_n$  may contain non-terminals as well as registers.

This application is more special than for general term rewriting systems. A *BE-substitution*  $\sigma$  is just a renaming of non-terminals to registers. A term  $t_1$  *BE-matches* a term  $t_2$  if there is a BE-substitution  $\sigma$  such that  $\sigma(t_1) = t_2$ , i.e.  $t_1$  and  $t_2$  are equal up to renaming of non-terminals. This allows to use any optimizing register allocation algorithm that fullfills the constraint, that no value containing register is reassigned. A full formal definition can again be found in [31].

#### 3 Correctness of TRS-based code generation

In [31], we reduced the correctness condition for BURS-based compiler back-ends to the following two local correctness conditions:

(i) A term-rewrite rule  $t \Rightarrow X$ ;  $\{m_1, \ldots, m_n\}$  is *locally correct* iff for every state q there are states  $q_1, \ldots, q_n$  such that

$$q \stackrel{m_1}{\to} q_1 \stackrel{m_2}{\to} q_2 \cdots \stackrel{m_n}{\to} q_n$$

and  $[eval(t)]_q = [content(\sigma(X))]_{q_n}$  where  $\sigma(X)$  is the register assigned to X.

(ii) A term-rewrite rule  $t \Rightarrow \bullet$ ;  $\{m_1, \ldots, m_n\}$  is *locally correct* iff for every state q there are states  $q_1, \ldots, q_n$  such that

$$q \stackrel{m_1}{\to} q_1 \stackrel{m_2}{\to} q_2 \cdots \stackrel{m_1}{\to} q_n$$

and  $content_{q_n} = content_{q'}$ ,  $content_{q_n}(R) = content_q(R)$  for all locked registers, and  $PC_{q_n} = PC_{q'}$  where q' is the state such that  $q \stackrel{t}{\to} q'$ .

Remark 1. In [31] we showed that it is possible to express the operational semantics of the intermediate language with the state space of the processor (except instruction pointers). This includes the memory mapping of the intermediate language onto the machine memory and storing environment pointers in certain registers. These registers are *locked*. Clever register assignment algorithms may lock more registers. The set of locked registers may be different for different program points. The operational semantics of the intermediate language using the state space of the processors allows to use machine-instructions as well as intermediate language instructions. Therefore, the state space of the states used in the local correctness conditions (i) and (ii) is equal. For the rest of this paper, we always assume this equality of state spaces.

The basic result we use in this paper is the

**Theorem 1.** Let S be a BURS-specification that specifies the transformation of basicblock graphs into machine code of a register machine. If every term-rewrite rule  $r : t \Rightarrow X; \{m_1, \ldots, m_n\} \in S$  is applied to expression trees only if no register occuring outside of t is assigned to the free non-terminals of r, no locked register is assigned to the free non-terminals of r and every term-rewrite rule satisfies (i) and (ii), then the BURS-specification specifies a correct compilation.

Thus, if a correct back-end generator applies the TR-rules conditionally (with the requirements on register assignment), and (i) and (ii) is satisfied for each TR-rule of a BURSspecification, then a correct compiler back-end is generated.

Figure 2. Verified Back-End Generator Architecture

#### 4 Proof Strategies for Local Correctness

This section consists of three parts. First we give two proof strategies related to local correctness conditions (i), and (ii). Then we show two examples applying these two proof strategies, respectively. Finally, we show that the application of these proof strategies to an erroneous term-rewrite rule.

Consider a term-rewrite rule  $r : t \Rightarrow X; \{m_1, \ldots, m_n\}$  the local correctness condition (i). It specifies a finite execution of ASM-transition rules and the application of an *eval*-macro. Since the latter must define a noetherian and confluent rewrite system, the number of macro applications is also finite. Therefore the proof strategy for (i) is

- 1. Apply symbolically (using the non-terminals occuring in t) the eval-macro,

- 2. Apply symbolically (using the non-terminals occuring in t and  $\{m_1, \ldots, m_n\}$ ) the state transitions of the ASM for the target machine

- 3. If content(X) = eval(t) then (i) is satisfied. Otherwise, output both terms.

**Theorem 2.** The above proof strategy is correct for term-rewrite rules  $r : t \Rightarrow X; \{m_1, \ldots, m_n\}$  where  $X \neq \bullet$ .

*Proof.* In any program, if r is applied onto a term t', then there is a register substitution  $\sigma$  such that  $\sigma(t) = t'$  (i.e.  $\sigma$  substitutes non-terminals by registers). Consider a symbolic update  $f(X_1, \ldots, X_n) := g(Y_1, \ldots, Y_n)$  performed in a state transition of the second step. Then the execution of the program performs the update  $f(\sigma(X_1), \ldots, \sigma(X_n)) :=$  $g(\sigma(Y_1), \ldots, \sigma(Y_n))$ . A similar argument applies to the application of the *eval*-macro. Thus, it holds  $[content(\sigma(X))]_{q_n} = [eval(\sigma(t))]_q$ . Therefore, the symbolic equality in the third step implies  $[content(\sigma(X))]_{q_n} = [eval(\sigma(t))]_q$ , i.e. (i) holds.

**Example 1.** Consider the term-rewrite rule add : intadd  $(X, Y) \Rightarrow Z$ ; {ADD X, Y, Z} where ADD is a DEC-Alpha instruction. The first step yields

$eval(intadd(X, Y)) = eval(X) \oplus_I eval(Y)$ =  $content(X) \oplus_I content(Y)$

The second step applies the state transition  $content(Z) := content(X) \oplus_I content(Y)$  of the ADD-instruction. Thus, after the symbolic execution of ADD X, Y, Z, it is  $content(Z) = content(X) \oplus_I content(Y)$ . Thus, the two terms to be compared in the third step are equal and the term-rewrite rule add is locally correct.

Thus, if the symbolic equality cannot be proven, the strategy postulates an equality that must always be satisfied in order to ensure (i). Thus, without algebraic identities such as the commutativity of  $\oplus_I$ , the proof strategy would also be complete: Suppose, that the strategy outputs that (i) is not satisfied. Then, we have to show that there is a state q, a term t' where r can be applied, and a valid register assignment such that (i) is violated, i.e.  $[eval(t')]_q \neq [content(\sigma(X))]_q$ . Suppose steps 1 and 2 show that  $eval(t) \neq content(X)$ . Observe that content(X) = s using the non-terminals occuring in t. Let  $\sigma$  be the substitution used when applying r such that  $\sigma t \neq \sigma s$ . Then it is easy that there are values of the registers such that these two expressions yield different results, i.e. (i) is violated. If  $\sigma t = \sigma s$  for all substitutions, then it is must be s = t, contradicting our assumption  $s \neq t$ .

Consider now the term-rewrite rules of the form  $t \Rightarrow \bullet; \{m_1, \ldots, m_n\}$ . Then, the following proof strategy is used:

- 1. Execute symbolically (using the non-terminals in t) the state transitions for t in the intermediate language ASM.

- 2. Execute symbolically  $\{m_1, \ldots, m_n\}$  in the machine language ASM.

- 3. For all non-terminals of t, compare symbolically content(X) after the first and the second step. Also compare content(R) for locked registers. If all of them are equal, then (ii) is satisfied. Otherwise, output the inequalities.

**Theorem 3.** The above proof strategy is correct for term-rewrite rules  $r : t \Rightarrow \bullet; \{m_1, \ldots, m_n\}.$

*Proof.* (Sketch) The proof is analogous to the proof of Theorem 2. The only difference is that more comparisons have to be done, and that for every states q,  $q_n$ , and q' as defined by local correctness condition (ii) the instruction pointers point to the same instruction if just r is applied. Let  $\pi$  be a program and  $\pi'$  be the program where r is applied onto a term t'. Since r defines a local replacement, the instruction after t' in  $\pi$  and the instruction after  $m_n$  in  $\pi'$  is the same.

To show a more complex proof, we give an example with a bit more complicated bit manipulation. Consider the generation of a 32 bit constant:

#### Example 2.

$$intconst(i32) \longrightarrow X; \{ LDA (T1, i32.L, R31, "L") \\ ZBI (T1, \#1111100_2, T1) \\ LDA (X, i32.H, T1, "H") \}$$

The coding of 32 bit integer constants uses the machine instructions "load-address" (LDA) and "zero-bytes-immediate" (ZBI). LDA loads the integer value that results from the addition of the second operand and the immediate value, which is shifted by 16 according to the type parameter, into the first operand. "zero-bytes" sets some bit patterns to zero according to the immediate value.

For the purposes of the simulation proof we need some definitions for the integer constant:

| i32            | $= hhll_{256}$              | That means w               | ve have:                                    |

|----------------|-----------------------------|----------------------------|---------------------------------------------|

| $\mathbf{s}_l$ | $=(i32)\langle 15\rangle$   | i32.L                      | $= 0011_{256}$                              |

| $\mathbf{s}_h$ | $=(i32)\langle 31\rangle$   | i32.H                      | $= 00 hh_{256}$                             |

| i32.L          | $=(i32)\langle 0:15\rangle$ | $Sext_{16}$ (i32.L)        | $= s_l s_l s_l s_l s_l s_l s_l s_l s_l s_l$ |

| i32.H          | $=(i32)\langle 16:31 angle$ | Sext <sub>16</sub> (i32.H) | $= s_h s_h s_h s_h s_h s_h s_h h h_{256}$   |

"i32.L" denotes the lower 16 bit of the lower word (value "ll"), "i32.H" denotes the upper 16 bit of the lower word (value "hh").  $Sext_k(Y)$  extends the kth bit of Y to 64 bit.  $X\langle i \rangle$  addresses the *i*th bit of X.

The proof obligations can be formulated in the same way like before. The proof itself is more tedious but is nevertheless a straightforward simulation:

| rule application                                                                                                                                                                                                          | T1                                                                                                      | Х                                                                             | $\operatorname{state}$ |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|------------------------|

| LDA T1, i32.L, R31, "L"                                                                                                                                                                                                   |                                                                                                         |                                                                               |                        |

| $\operatorname{content}(\operatorname{T1}) := \operatorname{content}(\operatorname{R31}) \oplus_I Sext_{16} \ (\mathrm{i32.L})$                                                                                           |                                                                                                         |                                                                               |                        |

| $\operatorname{content}(\mathrm{T1}) := 0 \oplus_I Sext_{16} \ (\mathrm{i32.L})$                                                                                                                                          |                                                                                                         |                                                                               |                        |

| $\operatorname{content}(\mathrm{T1}) := Sext_{16} \ (\mathrm{i32.L})$                                                                                                                                                     | $\mathbf{s}_l  \mathbf{s}_l  \mathbf{s}_l  \mathbf{s}_l  \mathbf{s}_l  \mathbf{s}_l  \mathbf{ll}_{256}$ |                                                                               | $q'_1$                 |

| ZBI T1, $\#11111100_2$ , T1                                                                                                                                                                                               |                                                                                                         |                                                                               |                        |

| $\operatorname{content}(\mathrm{T1}) := \operatorname{ByteZap} (\operatorname{content}(\mathrm{T1}), \#11111100_2)$                                                                                                       |                                                                                                         |                                                                               |                        |

| $\operatorname{content}(\mathrm{T1})\langle \mathbf{i} \rangle := \begin{cases} \operatorname{content}(T1)\langle \mathbf{i} \rangle \ \operatorname{case} \ 0 \le i \le 15\\ 0_2 \ \operatorname{otherwise} \end{cases}$ | $00000011_{256}$                                                                                        |                                                                               | $q'_3$                 |

| LDA X, i32.H, T1, "H"                                                                                                                                                                                                     |                                                                                                         |                                                                               |                        |

| $\operatorname{content}(\mathbf{X}) := \operatorname{content}(\mathbf{T}1) \oplus_I \operatorname{LogShift}_L(\operatorname{Sext}_{16}(\operatorname{i32.H}), \operatorname{16})$                                         |                                                                                                         |                                                                               |                        |

| $\operatorname{content}(\mathrm{X}) := \operatorname{content}(\mathrm{T1}) \oplus_I \operatorname{s}_h \operatorname{s}_h \operatorname{s}_h \operatorname{s}_h \operatorname{hh00}_{256}$                                |                                                                                                         |                                                                               |                        |

| $\operatorname{content}(X)$                                                                                                                                                                                               |                                                                                                         | $\mathbf{s}_h  \mathbf{s}_h  \mathbf{s}_h  \mathbf{s}_h  \mathbf{hhll}_{256}$ | $q'_3$                 |

The last line of the simulation table proves our assumption correct. T1 and X can contain any preassigned value.

#### 5 Implementation of Proof Strategies and Error Detection in PVS

Beneath careless mistakes in combining instructions or operand ordering, bit-manipulations in sequences of instructions are the most erroneous kind of code. An example taken from our own specification development cycle is the rewrite rule for large integer constants, where happened to be some nontrivial bit-manipulation errors.

As an example, how PVS can help detecting errors we present the incorrect rule for large integer constants which has been used in a first attempt:

$intconst(i32) \longrightarrow X; \{ LDA (T1, i32.L, R31, "L") \\ LDA (X, i32.H, T1, "H") \}$

The formalization in PVS looks like:

```

medium_int_const : LEMMA (r0 /= r3) IMPLIES

bv2int[32](eval(intconstS(val32), rho(ms))) =

LET final = bb_interp(

cons(store(LDA(0), r3, 31, val32^(15,0)),

cons(store(LDA(1), r0, r3, val32^(31,16)), null))), ms)

IN bv2int[64](IntReg(final)(r0))

```

This rule does incorrectly treat sign extensions if the most-significant-bit (MSB) of the lower word is set. Invoking strategy (simul), the prover stops in the following situation:

A more compact notation for this equality is

$val = val(31, 16) \circ 0_{16} \oplus_I (s_{15})_{16} \circ val(15, 0)$

(" $\circ$ " denotes bit sequence concatenation). Obviously, this equality holds only if the MSB of the lower word is 0, i.e.

$s_{15} = 0.$

The example given in the previous section contains the correct implementation where this erroneous sign extension is corrected with an ZBI (Zero Bytes) instruction.

In addition, some more proof obligations have to be discharged. For example, one has to prove that the instruction sequences above are valid basic blocks. When type-checking the theory, PVS automatically generates such a type correctness condition (TCC). The proof is easily established using the built-in (grind) strategy.

Sometimes, it is useful to have the possibility to step through each machine instruction interactively. If one likes to see the effect of each instruction separately, one may use strategy (one-stp). First, the necessary rewrite rules have to be established using (init), then each execution of an instruction is invoked using (one-stp) which expands the definition of the basic block interpreter and then applies the rewrite rules and decision procedures.

#### 6 Conclusions

In this article we showed how to prove the local rewrite rules for language transformations correct with a symbolic simulation proof technique. The task is no longer to find a proof magically but we gave an constructive approach for proving rewrite rules. The correctness is proved w.r.t. operational semantics of both, intermediate and target language. The tool performs the proofs strategies mechanically using the proof checker PVS. Thus, the integration of such a prover with BURS back-end generators can guarantee – together with the correctness of a generator – the correctness of a compiler back-end. Moreover we showed that useful hints to errors in TRS-rules can be given. First results indicate that the quality of the binary machine code generated by correct compiler back-ends described in this paper is comparable to

|       |             | DEC-Alpha                |                    |                          | Intel-Pentium      |                          | SIMP              |                       |

|-------|-------------|--------------------------|--------------------|--------------------------|--------------------|--------------------------|-------------------|-----------------------|

|       |             | Ver                      | ifix               | C-Con                    | npiler             | C-Compiler               |                   | AM in C               |

| Iter  | ations      | $\operatorname{non-opt}$ | opt                | $\operatorname{non-opt}$ | opt                | $\operatorname{non-opt}$ | opt               | $\min$                |

| Loop  | 10000       | $0.57\mathrm{ms}$        | $0.57 \mathrm{ms}$ | $0.35 \mathrm{ms}$       | $0.31 \mathrm{ms}$ | $0.62 \mathrm{ms}$       | $0.50\mathrm{ms}$ | 5.0s                  |

|       | $100{ m M}$ | 5.72s                    | 5.70s              | 3.49s                    | $3.05 \mathrm{s}$  | 6.12s                    | 5.04s             | $13 h 53 m^*$         |

| Sieve | 1           | $1.63\mathrm{ms}$        | $1.23 \mathrm{ms}$ | $0.82\mathrm{ms}$        | $0.56 \mathrm{ms}$ | $1.02 \mathrm{ms}$       | $0.89\mathrm{ms}$ | 4.00s                 |

|       | 10000       | 16.35s                   | 12.26s             | 8.25s                    | 5.65s              | $10.23 \mathrm{s}$       | 8.94s             | $11 \mathrm{h6m^{*}}$ |

DEC-Alpha:

DEC-AXP(233MHz), OSF1, CC: DEC(V4.2)

Intel-Pentium:

Pentium(133MHz), Linux, CC: GNU(V2.7.0)

SIMP:

Pentium, execution times taken from [7], abstract machine implemented in C

Iterations:

Loop: loop iterations, Siew: searching the primes less than thousand, n times repeated SIMP: line 1 from [7], line 2 extrapolotion(\*) on repeated iterations

Optimization (opt)/Verifix: Peephole, C: Option -O4, SIMP: minimal execution times

Table1. Comparison of the Performance of the Machine Code generated by Correct Compilers

standard compilers and therefore orders of magnitudes faster than code generated by correct compilers constructed by other approaches [25,7]. Table 1 shows the comparison between our approach, the approach in [7] (SIMP), and a standard unverified C-compiler. Loop is a program that initializes a variable with a positive integer and decrements this integer by one until the content of this variable is zero, Sieve implements the sieve of Erastothenes. The complete test scenario can be found in [11].

Our aim is to integrate more and more established compilation techniques. If a library of correct data structures, algorithms, and generators is provided, then for the correctness of any transformation of one intermediate language to another, it will be sufficient to prove local correctness properties of transformation rules similar to those of term-rewrite rules.

The above performance results show that this approach seems feasible to construct realistic correct compilers compiling programs of real-life programming languages into binary machine code of real processors, and produce efficient code.

Acknowledgements: This work is supported by the *Deutsche Forschungsgemeinschaft* project Go 323/3-1 Verifix (Construction of Correct Compilers). We are grateful to our collegues in Verifix.

#### References

- E. Börger and D. Rosenzweig. The WAM-definition and Compiler Correctness. Technical Report TR-14/92, Dip. di informatica, Univ. Pisa, Italy, 1992.

- Egon Börger, Igor Durdanovic, and Dean Rosenzweig. Occam: Specification and Compiler Correctness.Part I: The Primary Model. In U. Montanari and E.-R. Olderog, editors, Proc. Procomet'94 (IFIP TC2 Working Conference on Programming Concepts, Methods and Calculi). North-Holland, 1994.

- 3. E. Brger and I. Durdanovic. Correctness of compiling occam to transputer. The Computer Journal, 39(1):52-92, 1996.

- D. F. Brown, H. Moura, and D. A. Watt. Actress: an action semantics directed compiler generator. In Compiler Compilers 92, volume 641 of Lecture Notes in Computer Science, 1992.

- B. Buth, K.-H. Buth, M. Fränzle, B. v. Karger, Y. Lakhneche, H. Langmaack, and M. Müller-Olm. Provably correct compiler development and implementation. In U. Kastens and P. Pfahler, editors, *Compiler Construction*, volume 641 of *Lecture Notes in Computer Science*. Springer-Verlag, 1992.

- Bettina Buth and Markus Müller-Olm. Provably Correct Compiler Implementation. In *Tutorial Material Formal Methods Europe '93*, pages 451–465, Denmark, April 1993. IFAD Odense Teknikum.

- 7. S. Diehl. Semantics-Directed Generation of Compilers and Abstract Machines. PhD thesis, Universität Saarbrücken, 1996.

- 8. Axel Dold. Representing the Alpha Processor Family using PVS. Verifix Working Paper [Verifix / Uni Ulm / 4.1], Universität Ulm, November 1995.

- 9. H. Emmelmann. Code selection by regularly controled term rewriting. In R. Giegerich and S.L. Graham, editors, *Code Generation Concepts, Tools, Techniques*, Workshops in Computing. Springer-Verlag, 1992.

- H. Emmelmann, F.-W. Schröer, and R. Landwehr. Beg a generator for efficient back ends. In ACM Proceedings of the Sigplan Conference on Programming Language Design and Implementation, June 1989.

- 11. T.S. Gaul. Bechmarking code-generation for IS to DEC-Alpha. Verifix Working Paper [Veri-fix/UKA/11], University of Karlsruhe, 1996.

- T.S. Gaul, A. Heberle, and W. Zimmermann. An Evolving Algebra Specification of the Operational Semantics of MIS. Verifix Working Paper [Verifix/UKA/3], University of Karlsruhe, 1995.

- T.S. Gaul and W. Zimmermann. An Evolving Algebra for the Alpha Processor Family. Verifix Working Paper [Verifix/UKA/4], University of Karlsruhe, 1995.

- 14. Y. Gurevich. Evolving Algebras; A Tutorial Introduction. Bulletin EATCS, 43:264-284, 1991.

- Y. Gurevich. Evolving Algebras: Lipari Guide. In E. Börger, editor, Specification and Validation Methods. Oxford University Press, 1995.

- C.A.R. Hoare, He Jifeng, and A. Sampaio. Normal Form Approach to Compiler Design. Acta Informatica, 30:701-739, 1993.

- J. McCarthy and J.A. Painter. Correctness of a compiler for arithmetical expressions. In J.T. Schwartz, editor, Proceedings of a Symposium in Applied Mathematics, 19, Mathematical Aspects of Computer Science. American Mathematical Society, 1967.

- P. D. Mosses. Abstract semantic algebras. In D. Bjørner, editor, Formal description of programming concepts II, pages 63-88. IFIP IC-2 Working Conference, North Holland, 1982.

- 19. P. D. Mosses. Action Semantics. Cambridge University Press, 1992.

- Markus Müller-Olm. An Exercise in Compiler Verification. Internal report, CS Department, University of Kiel, 1995.

- 21. Markus Müller-Olm. Modular Compiler Verification. PhD thesis, Techn. Fakultät der Christian-Albrechts-Universität, Kiel, June 1996. Erscheint als LNCS Band im Springer-Verlag.

- 22. Albert Nymeyer and Joost-Pieter Katoen. Code Generation based on formal BURS theory and heuristic search. Technical report inf 95-42, University of Twente, 1996.

- 23. Albert Nymeyer, Joost-Pieter Katoen, Ymte Westra, and Henk Alblas. Code Generation = A\* + BURS. In Tibor Gyimothy, editor, Compiler Construction (CC), volume 1060 of Lecture Notes in Computer Science, pages 160-176, Heidelberg, April 1996. Springer-Verlag.

- 24. S. Owre, J. M. Rushby, and N. Shankar. PVS: A Prototype Verification System. In Deepak Kapur, editor, Proceedings 11th International Conference on Automated Deduction CADE, volume 607 of Lecture Notes in Artificial Intelligence, pages 748-752, Saratoga, NY, October 1992. Springer-Verlag.

- J. Palsberg. An automatically generated and provably correct compiler for a subset of ada. In IEEE International Conference on Computer Languages, 1992.

- 26. L. Paulson. A compiler generator for semantic grammars. PhD thesis, Stanford University, 1981.

- Todd A. Proebsting. BURS automata generation. ACM Transactions on Programming Languages and Systems, 17(3):461-486, May 1995.

- 28. Richard L. Sites. Alpha Architecture Reference Manual. Digital Equipment Corporation, 1992.

- 29. W. Waite and G. Goos. *Compiler Construction*. Texts and Monographs in Computer Science. Springer, 1985.

- M. Wand. A semantic prototyping system. SIGPLAN Notices, 19(6):213-221, June 1984. SIG-PLAN 84 Symp. On Compiler Construction.

- W. Zimmermann and T. Gaul. On the Construction of Correct Compiler Back-Ends: An ASM Approach. Journal of Universal Computer Science, 3(5):504-567, 1997.

#### A Basic Block Graphs

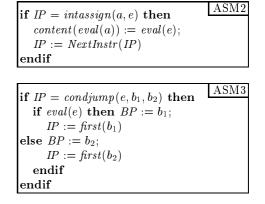

A BB-program is given by a set of basic blocks where each block consists of a sequence of instructions where the last one in a block is a jump or stop. INSTR denotes the universe of instructions. The data types used in this article are the type of 64-bit integers INT and the addresses ADDRon the target machine. VALUE denotes the union of all universes. Expressions are defined on these types and include only integer expressions and address expressions for simplicity. The universe EXPRdenotes all expressions. The complete abstract state machine specification can be found in [12]. Expressions are evaluated by eval :  $EXPR \rightarrow VALUE$  defined recursively over its structure (see ASM1).  $\oplus_A$ is the add operation on addresses of the machine, which is in our case equivalent to  $\oplus_I$ . Instructions consist of assignment instructions for different kind of expressions, jumps and procedure calls (ASM2).

Figure3. Basic block graphs

$\begin{array}{rcl} & & & & \\ & & eval(local(a)) \triangleq & content(eval(a)) \\ & & eval(intconst_i) \triangleq & i \\ & & eval(intadd(e_1,e_2)) \triangleq & eval(e_1) \oplus_I eval(e_2) \\ & & & \vdots \\ & & & \\ & & & eval(local(i)) \triangleq & local \oplus_A i \\ & & & eval(global(i)) \triangleq & global \oplus_A i \end{array}$

#### **B** The Dec-Alpha Processor Family

In this section we sketch the formal representation of the DEC-Alpha based on the more or less informal specification in the manufacturer manual [28].

The formalization shows parts of the derived abstract state machine specification. It includes the instruction set, addressing modes, register files and the memory, i.e. it models the programmer's view. More details can be found in [13] and [8]. The semantics of DEC-Alpha instructions are given by state transition functions. Dynamic functions of the abstract state machine constitute the state which consists of

Figure 4. State target machine

- the memory represented as a function  $mem : QUAD \rightarrow BYTE$ ,

- two register files, IntReg : REG for the available 32 integer registers and FloatReg : REG for 32 floating-point registers, and

- the program counter PC: QUAD.

#### ASM4

#### LOAD-ADDRESS

```

if cmd is LDA (ra, disp, rb, high)

then

if high="L"

then Content (ra) := Content (rb) \oplus_I Sext_{16} (disp)

else Content (ra) := Content (rb) \oplus_I LogShift_L (Sext_{16} (disp), 16)

endif

CurInstr := NextInstr (CurInstr)

endif

```

#### STORE

if cmd is ST (ra, disp, rb, type) then Content (Content (rb)  $\oplus_I$  Sext<sub>16</sub> (disp)) := Content (ra) CurInstr := NextInstr (CurInstr) endif

#### ADD-REGISTER

if cmd is ADD (ra, rb, rc, type) then Content (rc) := Content (ra)  $\oplus_I$  Content (rb) CurInstr := NextInstr (CurInstr) endif

ASM7

#### ZERO-BYTES-IMMEDIATE

The addressable memory unit is a byte. In order to load and store quadwords – the usual integer type for DEC-Alpha architectures – or floats we introduce the function  $Content : QUAD \cup REG \rightarrow VALUE$  which loads and stores 8 bytes from/into memory. For example, fetching a quadword or float from memory is carried out by concatenating 8 subsequent bytes starting at the given address.

The DEC-Alpha is a typical "load-store" architecture, what means that the only memory accessing functions are load and store instructions, addresses are given register relative. Some examples are given in ASM4-7, auxiliary functions have the following definition:

ByteZap results operand op1 with byte n set to zero, if bit n of operand op2 is set:

$$(ByteZap(op1, op2))\langle 8*n+7:8*n\rangle = \begin{cases} (op1)\langle 8*n+7:8*n\rangle: & (op2)\langle n\rangle = 0_2\\ 0_2^8: & otherwise \end{cases}$$

$Sext_k(X)$  returns operand X sign extended from bit k to 64 bits.  $Zext_k(X)$  returns operand X zero extended from bit k to 64 bits.

ASM6

ASM5

## NUSMV: a reimplementation of SMV

Alessandro Cimatti<sup>1</sup> Ed Clarke<sup>2</sup> Fausto Giunchiglia<sup>1</sup> Marco Roveri<sup>1,3</sup>

#### Abstract

This paper describes the first results of a joint project between CMU and IRST whose goal is to produce a reimplementation of SMV. The idea is that this new model checker, called NUSMV, should be usable, customizable and extensible, with as little effort as possible, also by people different from the developers. A further goal is to produce a system which is very robust, and close to the standards required by industry.

### 1 Introduction

This paper describes the first results of a joint project between CMU and IRST whose goal is to produce a reimplementation of SMV [11]. The new model checker, called NUSMV, is designed to be a well structured, flexible and documented platform, and should be usable, customizable and extensible with as little effort as possible also from people different from the developers. Furthermore, in order to make NUSMV applicable in technology transfer projects, it was designed to be very robust, close to the standards required by industry, and to allow for expressive specification languages.

With respect to SMV, NUSMV is being upgraded along three dimensions, namely:

- quality of the implementation. This will allow us to have a system which is very robust, and whose code is well documented, easy to understand and modify.

- system architecture. This will allow us to have a system whose architecture is very modular (thus allowing the substitution or elimination of certain modules) and open (thus allowing the addition of new modules). A further feature is that in NUSMV the user can control, and possibly change, the order of execution of some of the system modules.

• system functionalities. This will allow us to have a system with more user functionalities (e.g., multiple interfaces, a simulation mode) and more heuristics for, e.g., achieving efficiency or partially controlling the state explosion.

The first two dimensions involve a lot of software engineering and are instrumental to the third. NUSMV is currently being beta-tested, and will be shortly distributed publicly in the Web. Our work will then concentrate on adding new functionalities, possibly developed by other groups. We briefly describe the implementation, architecture and functionalities of NUSMV in Sections 2, 3, and 4, respectively.

### 2 Implementation

The implementation of NUSMV has the following features:

- 1. NUSMV is written in ANSI C and is POSIX compliant. This makes the system portable to any platform compliant with these standards. NUSMV has been throughly debugged with Purify<sup>1</sup> to detect memory leaks and runtime memory corruption errors.

- 2. The code of NUSMV has been documented following the standards of the EXT system<sup>2</sup>. This allows for the automatic extraction of the documentation from the comments in the system code. The documentation (e.g. the *User Manual*, the *Tutorial*, the *Programmer Manual*) will be available in different formats (for instance POSTSCRIPT, DVI, PDF, INFO, HTML and TXT), directly from the NUSMV interaction shell (see below), via an HTML viewer or in hardcopy.

- 3. A kernel has been isolated which provides the low level functionalities such as dynamic memory allocation, and manipulation of basic data structures (e.g. cons cells, hash tables). The kernel also encapsulates the state of the art CUDD binary decision diagrams (BDD) package developed at Colorado University [13]. This kernel can be used as a black box, following coding standards which have been precisely defined.

<sup>&</sup>lt;sup>1</sup>Purify is a commercial product for run-time error detection. More information on this tool can be found at the url "http://www.pureatria.com".

<sup>&</sup>lt;sup>2</sup>The EXT system is a set of programs that generate documentation for the World-Wide Web from specially-formatted C programs. These are being used in a variety of large software projects and have been shown to simplify the programmer's task. More information about this documentation tool can be found at the url "http://www.alumni.caltech.edu/~sedwards/ext"

4. In order to implement a top level interaction shell, the code of NUSMV was separated in different packages, each implementing a set of related functionalities. Each package is associated with a set of commands which can be interpreted by the NUSMV interaction shell. The implementation of the interaction shell required the definition and implementation of an error trapping mechanism (SMV exits if any kind of error occurs).

### 3 Architecture

The architecture of NUSMV is organized in the following modules:

- 1. The parsing routines, which process a file written in SMV language, build a parse tree representing the internal format of the input language, and check its syntactic correctness.

- 2. The routines for the encoding of data types and finite ranges into boolean domains. Different encoding policies can be more appropriate for different kinds of variables (e.g. control path, data path). Currently only the standard SMV encoding is possible. The separation of the encoding procedures will allow for the integration in the same architecture of other forms of encoding, e.g. those used in Word-Level SMV ([5]).

- 3. The model compiler, which from the parse tree builds the finite state machine (FSM) representing the model (e.g. the transition relation, the initial states, the fairness conditions).

- 4. The routines for constructing and manipulating FSM's. FSM's can be represented in monolithic or partitioned form [10]. The interface to other modules is given by the primitives for the computation of image and counter-image of sets of states.

- 5. The reachability and model checking routines. These are independent of the particular method used for representing the FSM. They use the routines for computing image and counter-image which are independent of the actual partitioning method used.

- 6. The routines for counterexample and witness generation and inspection. Counterexamples and witnesses can be produced with different levels of verbosity, in the form of reusable data structures, and can subsequently be inspected and navigated.

- 7. The interaction with the user, which has two modes. The first is the usual SMV batch mode, where the different computation steps (e.g. parsing, model construction, reachability, model checking) are activated according

to a fixed, predefined algorithm. The other (new) mode is a top level interaction shell. Through the shell the user can activate, as system commands with different options, various NUSMV computation steps, which can therefore be invoked separately, possibly undone, and repeated under different modalities. These steps include the definition of a FSM, the parsing and model checking of CTL formulae, and the configuration of the BDD package. For instance, several automatic variable ordering methods and cache configuration mechanisms can be suitably tuned according to the application.

Most of the features described above were already present in SMV. In NUSMV, however, all the code has been restructured to be organized according to the system architecture described in this section. Substantial recoding has been done in order to achieve the architectural separation of the modules, in particular of the kernel and the model compiler. New code has been added for the implementation of the user interface.

### 4 Functionalities

With respect to SMV, the following functionalities have been added:

- 1. NUSMV can perform enhanced reachability analysis. Specialized routines allow for checking invariants, i.e., formulae which must hold uniformly on the model, on the fly.

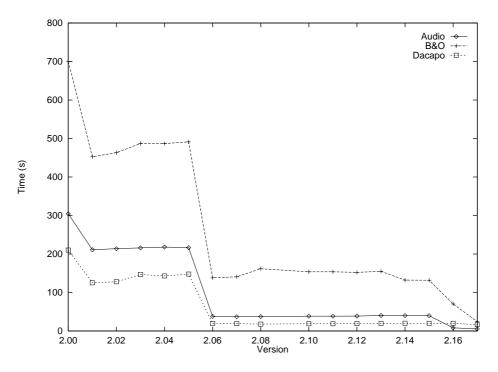

- 2. NUSMV allows for the conjunctive and disjunctive partitioning of the model [10], and inspection and definition of a suitable order of partitions according to the heuristics defined in [7] and in [12].