# BRICS

**Basic Research in Computer Science**

Proceedings of the Workshop on

# Formal Approaches to Testing of Software FATES'01

Aalborg, Denmark, August 25, 2001

Ed Brinksma Jan Tretmans (editors)

**BRICS Notes Series**

NS-01-4

ISSN 0909-3206

August 2001

Copyright © 2001, Ed Brinksma & Jan Tretmans

(editors).

BRICS, Department of Computer Science University of Aarhus. All rights reserved.

Reproduction of all or part of this work is permitted for educational or research use on condition that this copyright notice is included in any copy.

See back inner page for a list of recent BRICS Notes Series publications. Copies may be obtained by contacting:

**BRICS**

Department of Computer Science University of Aarhus Ny Munkegade, building 540 DK-8000 Aarhus C Denmark

Telephone: +45 8942 3360 Telefax: +45 8942 3255 Internet: BRICS@brics.dk

BRICS publications are in general accessible through the World Wide Web and anonymous FTP through these URLs:

http://www.brics.dk ftp://ftp.brics.dk

This document in subdirectory NS/01/4/

# Formal Approaches to Testing of Software

FATES'01 A Satellite Workshop of CONCUR'01 Aalborg, Denmark, August 25, 2001 Proceedings

# **Preface**

Testing is an important technique for validating and checking the correctness of software. However, effective and efficient testing turns out to be difficult, expensive, laborious, error-prone and time consuming. Formal methods are a way of specifying and verifying software systems by applying techniques from mathematics and logic. This enables the analysis of systems and the reasoning about them with mathematical precision and rigour. Formal methods and testing used to be a difficult combination. Formal methods aim at verifying and proving correctness, while testing can only show the presence of errors. Validation in practice is most often performed by testing, while academic research was concentrated on formal verification.

Recently, there is an increasing interest in the use of formal methods in software testing. It is recognized that formal methods and testing are complementary techniques which can, and should be used in combination. The use of formal methods can help in alleviating some of the challenges of software testing. In particular, a formal, and formally verified specification provides a more precise, more consistent and more complete starting point for the testing process and the obtained tests can be formally validated whether they test what should be tested. Moreover, the use of formal methods allows automating the generation of tests from formal specifications, thus leading to a faster, cheaper and less error-prone testing process. And finally, formal testing turns out to be a good starting point for introducing formal methods in software development.

The aim of the workshop FATES — Formal Approaches to Testing of Software — is to be a forum for researchers, developers and testers to present ideas about and discuss the use of formal methods in software testing. Topics of interest are formal test theory, test tools and applications of testing based on formal methods, including algorithmic generation of tests from formal specifications, test result analysis, test selection and coverage computation based on formal models, and all of this based on different formal methods, and applied in different application areas.

This volume contains the papers presented at FATES'01 which was held in Aalborg (Denmark) on August 25, 2001, as an affiliated workshop of CONCUR'01. Out of 18 submitted papers the programme committee selected 9 papers and 1 tool demonstration for presentation at the workshop. Together with the keynote presentation by David Lee from Bell Labs Research China they form the contents of these proceedings.

The papers present different approaches to using formal methods in software testing. The main theme is the generation of an efficient and effective set of test cases from a formal description. Different formalisms are used as the starting point, such as finite state machines, Z, Statecharts, SDL, constraint languages, grammars and timed

automata, and different algorithms are discussed for the generation process, ranging from formalization of the manual testing process to the (re)use of techniques from model checking.

The papers give insight in what has been achieved in the area of software testing with formal methods. Besides, they give clear indications of what has to be done before we can expect widespread use of formal techniques in software testing. The prospects for using formal methods to improve the quality and reduce the cost of software testing are good, but still more effort is needed, both in developing new theories and in making the existing methods and theories applicable, e.g., by providing tool support.

We would like to thank the programme committee and the additional reviewers for their support in selecting and composing the workshop programme, and we thank the authors for their contributions without which, of course, these proceedings would not exist.

Last, but not least, we thank Brian Nielsen and Arne Skou for arranging all local matters of organizing the workshop, Aalborg University for giving the opportunity to organize FATES'01 as a satellite of CONCUR'01, BRICS for supporting the printing and distribution of these proceedings, and Jan Feenstra en René de Vries for setting up the FATES'01 web page.

Enschede, August 2001

Ed Brinksma Jan Tretmans

# **Programme committee**

Ed Brinksma (University of Twente, The Netherlands), co-chair

Rocco De Nicola (Università degli Studi di Firenze, Italy)

Marie-Claude Gaudel (Université de Paris-Sud, France)

Jens Grabowski (Universität Lübeck, Germany)

Robert Hierons (Brunel University, United Kingdom)

Thierry Jéron (INRIA Rennes, France)

Doron Peled (Bell Laboratories, USA)

Alexandre Petrenko (CRIM, Canada)

Jan Tretmans (University of Twente, The Netherlands), co-chair

Antti Valmari (Tampere University of Technology, Finland)

Carsten Weise (Ericsson Eurolab Deutschland GmbH, Germany)

# Referees

Timo Aaltonen Ilkka Kokkarinen

Axel Belinfante Mieke Massink

Machiel van der Bijl Brian Nielsen

Sergiy Boroday Vlad Rusu

Pedro R. D'Argenio Ina Schieferdecker Michael Ebner Michael Schmitt Jan Feenstra Arne Skou

Stefan Heymer René G. de Vries

# **Organization**

Brian Nielsen,

Arne Skou,

Aalborg University,

Denmark

# **Contents**

| 1  | Efficient Algorithms for Test Sequence Selection                                                                               | 1   |

|----|--------------------------------------------------------------------------------------------------------------------------------|-----|

| 2  | Tool Demonstration Proposal: UML Validation Suite                                                                              | 9   |

| 3  | Automatic Test Generation from Statecharts using Model Checking .<br>Hyoung Seok Hong, Insup Lee, Oleg Sokolsky, Sung Deok Cha | 15  |

| 4  | Automatic Generation of Tests from Statechart Specifications Simon Burton, John Clark, John McDermid                           | 31  |

| 5  | Classical Search Strategies for Test Case Generation with Constraint Logic Programming                                         | 47  |

| 6  | Towards Formal Test Purposes                                                                                                   | 61  |

| 7  | Complexity Issues of Connectivity Testing                                                                                      | 77  |

| 8  | A Simple Approach to Testing Timed Systems                                                                                     | 93  |

| 9  | Test Case Characterisation by Regular Path Expressions                                                                         | 109 |

| 10 | Using SDL Tools to Test Properties of Distributed Systems                                                                      | 125 |

| 11 | A Formal Approach to Practical Test Selection                                                                                  | 141 |

# **Efficient Algorithms for Test Sequence Selection**

(Extended Abstract)

David Lee and Ruibing Hao

Bell Labs Research China, Beijing, China

**Abstract**: We study the test sequence selection problem. Given a large number of tests for a protocol system, we want to select a subset of tests so that the number of tests is reduced yet the test coverage is not sacrificed. We discuss the complexity of the test selection problem and propose a class of algorithms for different protocol system information requirements, test coverage criteria, and cost. This article is an extended abstract of [LH], and we refer the interested readers to the full paper for a detailed study and experimental results.

# 1. INTRODUCTION

With advanced computer technology protocol systems are getting larger to fulfil complicated tasks. However, they are also becoming less reliable. Testing is an indispensable part of system design and implementations; yet it has proved to be a formidable task for complex systems. Because of its practical importance and theoretical interest, there have been a lot of activities on protocol system testing. There are conformance testing, interoperability testing, and performance testing. Conformance testing is to test conformance of system implementations to their specifications [Br, LY1, PBG]. Interoperability testing tends to uncover faults when different system components are interoperating or interfacing with each other [GHLS, KK]. Conformance and interoperability testing are designed to check the correctness of system behaviors whereas performance testing is related to the system performance, such as its transmission rate.

For certain complicated legacy protocol systems, such as 5ESS (AT&T/Lucent No. 5 Electronic Switching System), tests have been generated and applied to the systems over the years at different development stages and by different test engineers. There are thousands of test sequences in the available test set. To test such systems, it is impractical to generate tests from scratch, since it is often impossible to model the systems because they are too complex. Therefore, we want to use the available test set accumulated over years. However, we do not want to execute all of them, since there are too many and to run each test takes a substantial amount of time. A natural solution in practice is to select test sequences among the available test set.

The test selection problem was studied in [LPB] based on the valuations of the test sequences to be selected, and it was reduced to an optimisation problem over Boolean algebra. For testing in context, the problem was studied in [YCL]. An important issue of test selection is the possible loss of coverage. This problem was investigated in [LPB] for partially specified machines and also in [CV, VC, ZV] with an elegant metric of coverage. The selection criteria and their notations were studied in [Pa].

In this paper, we study the following test selection problem. We have a large set of test sequences, and we want to select a minimal subset of tests to execute without sacrificing the fault coverage. For a formal study, we use extended finite state machine to model protocol systems. We discuss the complexity of the problem and propose efficient algorithms for the test sequence selection.

After describing an extended finite state machine model and its reachability graph, we formulate a problem of test sequence selection, discuss the coverage criteria, and study the problem complexity. We then discuss efficient algorithms for the test selection.

A finite state machine contains a finite number of states and produces outputs on state transitions after receiving inputs. It is often used to model control portions of protocol systems. However, data portions of protocols include variables and operations based on their values; ordinary finite state machines are not powerful enough to model in a succinct way the physical systems any more. Extended finite state machines (EFSM), which are finite state machines extended with variables, have emerged from the design and analysis of communication protocols [LY1]. For instance, IEEE 802.2 LLC [ANSI] is specified by 14 control states, a number of variables, and a set of transitions (pp. 75-117). For a formal definition of EFSM and the related concepts, see [LY1].

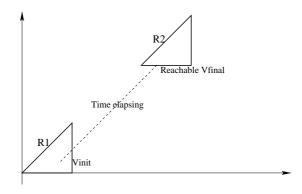

Each combination of a state and variable values is called a configuration. An EFSM usually has an initial state  $s_0$  and all the variables have an initial value  $\mathbf{x}_{init}$ ; we have the initial configuration ( $s_0$ ,  $\mathbf{x}_{init}$ ). A reachability graph consists of all the configurations and transitions, which are reachable from the initial configuration. It is a directed graph where the nodes and edges are the reachable configurations and transitions, respectively. Obviously, a control state may have multiple appearances in the nodes (along with different variable values) and each transition may appear many times as edges in the reachability graph.

For a path from the initial node (configuration) of the reachability graph, the input/output (I/O) labels on the transitions of the path provide an I/O sequence. Conversely, if an I/O sequence corresponds to a unique path from the initial node in the reachability graph, then the underlying EFSM is *deterministic*. Otherwise, it is *non-deterministic*. For clarity, in this paper we only consider systems, which are modelled by deterministic EFSM's. Our approaches can be modified to handle non-deterministic EFSM's, as we shall comment in the conclusion of the paper.

Given an input sequence, there is at most one path from the initial node in the reachability graph such that the transitions on the path are labelled with the input sequence, since the machine is deterministic. If such a path exists, then the given input sequence is *valid*. Otherwise, it is *invalid*. Obviously, a valid input sequence corresponds to a unique I/O sequence, which are the labels on the corresponding unique path from the initial node.

We first study the test selection problem, assuming that the underlying system reachability graph is available. We then relax the problem with an assumption that only the EFSM specification of the underlying system is available. Finally, we present algorithms for a general case when no information of the underlying system is available for test selection.

# 2. TEST SEQUENCE SELECTION PROBLEM AND ITS COMPLEXITY

A test sequence (or a scenario) is valid input sequence of a protocol system that is modelled by an EFSM. Since the system is deterministic, there is a one-to-one correspondence between test sequences and paths in the reachability graph from the initial configuration. In practice, a test sequence usually consists of an I/O sequence; the input sequence is applied to the system under test, and the output sequence is to be observed from the system response. Therefore, a test sequence can be represented by a valid input sequence, a valid I/O sequence, or a path from the initial configuration in the reachability graph of the underlying protocol system. For convenience, we shall use these terms interchangeably.

Informally, the test sequence selection problem is: Given a set of test sequences S, select from S a subset of tests S\* with a desirable fault coverage. Fault coverage is essential for testing. However, it is often specified differently from different system models and practical needs.

A commonly used criterion of fault coverage is to test each edge in the reachability graph at least once. It has been a well-accepted criterion in practice, and we first consider this criterion. Formally, given an EFSM  $\mathbf{M}$ , let G be its reachability graph with an initial configuration  $v_0$ , which corresponds to the initial state of  $\mathbf{M}$  and the initial variable values. A test sequence of  $\mathbf{M}$  is a path in G from  $v_0$ . A covering test set is a set of test sequences such that each edge of G is covered by at least one of the test sequences. We want to select a subset of tests such that it is still a covering test set and contains a minimal number of tests:

**Problem 1. Test selection with a reachability graph.** Given the reachability graph of an EFSM and a covering test set S, select a subset of test sequences  $S^*$  from S, such that  $S^*$  is a covering test set with a minimal cardinality.

The problem is NP-hard [LH]. Therefore, it is hard to obtain an optimal solution for test selection in general. We discuss heuristic methods next.

# 3. TEST SEQUENCE SELECTION

We first consider the case that the underlying system reachability graph is available, and then study the more general case without such reachability graphs.

# 3.1. Test Sequence Selection with a Reachability Graph

We consider the following greedy method. We first find a test sequence in S that covers a maximal number of uncovered edges of the reachability graph, and add this test to S\*. We then repeat the process until all the edges of the reachability graph are covered. Formally,

```

Algorithm 1.

input: reachability graph G and a covering test set S

output: a covering test set S*, which is a subset of S

1. mark all edges in graph G as uncovered;

2. S* = Λ; /* an empty set */

3. repeat

4. find a test sequence s in S that covers a maximal number of uncovered edges of the graph G, and mark these edges as covered;

5. S = S - {s}, S* = S* ∪{s};

6. until all edges in G are covered

```

Figure 1. Algorithm 1

A routine analysis shows that Algorithm 1 takes time O(MN) to select a covering test set where M and N are the total length and number of all the test sequences in the given covering test set.

To reduce the cost we may want to avoid examining all the tests in the set. We can conduct the following preprocessing and variations of Algorithm 1.

We first sort the tests in S according to their lengths in a descending order, and then examine them in that order. The rationale is: longer tests correspond to longer paths in the reachability graph and may cover more edges of the graph. Furthermore, if we have found a test, which covers k uncovered edges, then there is no need to examine tests of length k or less. Since there are N tests in the set, the added cost of sorting is O(NlogN), which is negligible since it is dominated by O(MN).

Randomisation often helps. We can select each test sequence to be examined from S uniformly at random.

Another variation is that we sort the test sequences by their input symbols alphabetically rather than their lengths, remove all the tests which are a proper prefix of other tests, and then apply Algorithm 1. Obviously, this pre-processing reduces redundant tests and we have fewer tests to process. We shall further discuss this variation in the next section.

# 3.2. Test Sequence Selection without a Reachability Graph

return S\*

Often we only have a test set available but do not have the corresponding reachability graph of the underlying system or it is too costly to construct such a graph. The problem becomes harder since we do not know whether a selected test set covers all the edges in the reachability graph.

Suppose we have the underlying system specification EFSM yet without its reachability graph. We have:

**Problem 2. Test selection with an EFSM.** Given an EFSM and a covering test set S, select a subset of test sequences  $S^*$  from S, such that  $S^*$  is a covering test set with a minimal cardinality.

Similar to Problem 1, the test selection problem 2 is NP-hard. Therefore, it is hard to obtain an optimal solution for test selection in general.

We can use the following heuristic procedure. We examine all the test sequences in S, trace each sequence in the EFSM, and record all the edges covered in the corresponding reachability graph. We then select test sequences in S until all the recorded edges are covered. The selection procedure is similar to Algorithm 1, and the variations of Algorithm 1 also apply here. Note that we do not construct the reachability graph explicitly.

```

Algorithm 2.

input: EFSM M and covering test set S

output: a covering test set S*, which is a subset of S

E = \Lambda; /* identify all edges of reachability graph; E is an empty edge set */

for each test sequence s_i in S, i = 1, ..., N

u=u_0=\langle s_0 | x_{init} \rangle; /* u_0 is the initial configuration of M */

for j = 1, ..., k_i /* k_i is the number of transitions in s_i */

4.

5.

trace transition t_{ij} in M and determine next configuration v;

if corresponding edge in reachability graph (u,v) \notin E

E = E \cup \{(u,v)\};

9. set all edges in set E as uncovered; /* find a covering subset S^* */

10. S^* = \Lambda; /* an empty set */

11. repeat

find a test sequence s in S that covers a maximal number of uncovered

edges in set E, and mark these edges as covered;

S = S - \{s\}, S^* = S^* \cup \{s\};

14. until all edges in E are covered

15. return S*

```

Figure 2. Algorithm 2

Algorithm 2 takes time O(MNlogM) to select a covering test set where M and N are the total length and number of all the test sequences in the given covering test set.

Algorithm 2 is for a more general test selection Problem 2 where there is no reachability graph and also no need to construct one. However, there is an extra price to pay in terms of the run time, i.e., a factor of logM.

Often in practice the underlying system model may not be available, especially for those legacy systems, and we only have a set of tests to select. This is the most general case of the test selection problem:

Problem 3. Test selection without any information of the underlying protocol system. Given a covering test set S for a protocol system, for which there is no information available, select a subset of test sequences  $S^*$ , such that  $S^*$  is a covering test set.

Different from Problem 1 and 2, in general it is impossible to select a minimal covering test set since there is no information of the underlying protocol system.

For this problem we only consider the following redundancy criterion. Let s and s\* be two test sequences where s\* is a prefix of s. Let p and p\* be the corresponding paths from the initial configuration in the reachability graph, which we do not know. Since the corresponding EFSM

is deterministic,  $p^*$  is a prefix of p as paths in the reachability graph, and we can remove  $s^*$  from the test set without sacrificing the coverage. Consequently, if S is a covering test set, the test subset  $S^*$ , selected by discarding all the prefixes, is still a covering test set. As a matter of fact, in the worst case, we cannot reduce the tests anymore. Consider the following reachability graph. It consists of separate paths from the initial node. For test selection, we can only discard the paths (tests), which are a proper prefix of another path; any further reduction will lose the coverage.

The above observations lead to the following algorithm. Consider the alphabet set of all the input symbols. We sort all the input sequences in S alphabetically and then remove all the input sequences (test sequences), which is a prefix of another input sequence.

```

Algorithm 3.

input: test sequence set S and alphabet set of all the input symbols \Sigma output: subset S^* of S with redundant tests removed

1. sort all input sequences of S alphabetically;

2. S^* = \Lambda; /* an empty set */

3. for i = 1, ..., N-1 /* N is the cardinality of S */

4. if s_i is not a prefix of s_{i+1}

5. S^* = S^* \cup \{s_i\};

6. S^* = S^* \cup \{s_N\};

7. return S^*

```

Figure 3. Algorithm 3

Given a test set S, Algorithm 3 removes redundant tests and selects a subset of tests  $S^*$ . If S is a covering test set of the reachability graph of the underlying protocol system, then  $S^*$  remains a covering test set.

Note that Algorithm 3 may select test sequences that are redundant in terms of covering the reachability graph since we do not have its information. Therefore, the resulting number of tests may be larger than that from Algorithm 1 and 2.

It takes time O(MlogN) to select tests using Algorithm 3 where M and N are the total length and number of all the test sequences in the given test set.

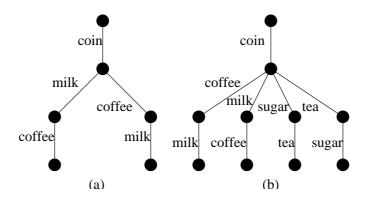

The cost of the test selection of Algorithm 3 is dominated by sorting the test sequences. We now discuss another method, using trees. It is optimal in terms of run time; it takes time proportional to the total lengths of the test sequences to be selected.

We grow a tree as follows. Initially, we have a root node  $v_0$ . Each edge is labeled with an input symbol. For each input sequence (test), we walk down the tree as follows. At a node u of the tree with an input symbol a in the sequence, if there is an outgoing edge from u labeled with a, then we walk down along that edge, arrive at the end node v, and process the input symbol in the test sequence after a. However, if there are no outgoing edges labeled with a, then we add a tree edge (u,v) from u, label it with a, walk down along (u,v), and continue processing from v as before. Each test requires a tree walk. After all the tests have been processed, we can obtain the selected tests as follows. We only have to select the tests (or paths) from the root to a leaf node; all the other tests (paths) a prefix of these selected tests. Note that each step of the tree walk takes a constant time (if we have a bitmap at each node to keep track of the labels of all the

outgoing edges). Therefore, it takes time proportional to the length of a test sequence to process. Hence the total cost is O(M).

It takes time O(M) to select tests using Algorithm 4 where M is the total length of all the test sequences in the given test set.

Obviously, Algorithm 4 removes the prefixes and selects the same test set as Algorithm 3. It is more efficient but involves an on-line tree construction process. Again, if the given test set is a covering set then the selected subset is also a covering. But it may contain redundant tests in terms of covering the reachability graph, of which we have no information.

```

Algorithm 4.

input: test sequence set S and alphabet set of all the input symbols \Sigma

output: subset S* of S with redundant tests removed

1. V = \{v_0\}; /* V is node set of tree T; each node keeps track of all input

symbols of its outgoing edges by a bitmap, */

for i = 1, ..., N /* N is the number of test sequences in S */

2.

u = v_0; /* a tree walk from initial node v_0 */

3.

4.

for j = 1, ..., k_i /* k_i is number of input symbols in sequence s_i */

let t_{ij} be transition of s_i under examination with input t_{ii}->a;

5.

if (u.bitmap(a)=0) /* not recorded yet */

6.

7.

initialize a new node v;

8.

construct a new tree edge (u, v);

u.bitmap(a) =1; /* record this input symbol at u */

10.

u = v; /* walk down tree to v along newly constructed edge */

else /* input has been recorded and tree edge exits for a walk */

11.

u=v:

13. S^* = \Lambda; /* an empty set */

14. for each leaf node v of tree T;

let s be test sequence corresponding to path from v_0 to v;

15.

16.

S^*=S^*\cup \{s\}:

17. return S*

```

Figure 4. Algorithm 4

# 4. **CONCLUSION**

In this paper, we have discussed the test sequence selection problem. Given a test sequence set, we want to select a subset of tests; without sacrificing the coverage we want to minimize the number of the selected tests to reduce the test execution time. We have proposed several algorithms with different required information and coverage, at different costs, and with different redundancy of the selected tests.

So far we assume that the underlying protocol system is deterministic, and in this case, a valid test sequence corresponds to a unique path in the reachability graph. If the system is non-deterministic, then a valid test sequence may correspond to multiple paths in the graph. Since the execution sequence is non-deterministic, the coverage of the edges in the reachability graph is probabilistic. While the union of all the possible paths, which are associated with a valid test sequence, is considered for coverage, we can only claim in a probabilistic sense.

# **ACKNOWLEDGEMENTS**

Kun Du from Peking University implemented some of the algorithms. Our thanks go to the reviewers of PSTV-FORTE'2001 for their constructive comments and suggestions.

#### REFERENCES

- [ANSI] International standard ISO 8802-2, ANSI/IEEE std 802.2, 1989.

- [Br] E. Brinksma, A Theory for the Derivation of Tests, Proc. PSTV, pp. 63-74, 1988.

- [BTV] E. Brinksma, J. Tretmans and L. Verhaard, A Framework for Test Selection, Proc. PSTV, pp. 233-248, 1991..

- [CV] J. A. Curgus and S. T. Vuong, A Metric Based Theory of Test Selection and Coverage, Proc. PSTV, 1993.

- [GJ] M. R. Garey and D. S. Johnson, Computers and Intractability: a Guide to the Theory of NP-Completeness, W. H. Freeman, 1979.

- [GHLS] N. Griffeth, R. Hao, D. Lee, and R. Sinha, *Integrated System Interoperability Testing with Applications to VoIP, Proc. FORTE/PSTV*, pp. 69-84, 2000.

- [KK] S. Kang and M. Kim, Interoperability Test Suite Derivation for Symmetric Communication Protocols, Proc. FORTE/PSTV, 57-72, 1997.

- [LH] D. Lee and R. Hao, Test Sequence Selection, Proc. PSTV-FORTE, 2001.

- [LY1] D. Lee and M. Yannakakis, *Principles and Methods of Testing Finite State Machines a Survey, The Proceedings of IEEE*, Vol. 84, No. 8, pp. 1089-1123, 1996.

- [LY2] D. Lee and M. Yannakakis, *Optimization Problems from Feature Testing of Communication Protocols*, *Proc. ICNP*, pp. 66-75, 1996.

- [LPB] G. Luo, A. Petrenko, and G. v. Bochmann, Selecting Test Sequences for Partially Specified Nondeterministic Finite State Machines, Proc. IFIP 7<sup>th</sup> Int. Workshop on Protocol Test Systems, 1994.

- [Mo] E. F. Moore, Gedanken-experiments on sequential machines, Automata Studies, Annals of Mathematics Studies, Princeton University Press, no.34, pp.129-153, 1956.

- [Pa] J. Pachl, A Notation for Specifying Test Selection Criteria, Proc. PSTV, pp. 71-84, 1990.

- [PY] C. H. Papadimitriou, M. Yannakakis, *Optimization, Approximation and Complexity Classes, J. Comp. Sys. Sc.*, 43(3), 425-440, 1991.

- [PBG] A. Petrenko, S. Boroday, R. Groz, Confirming Configurations in EFSM, Proc. FORTE/PSTV, 5-24, 1999.

- [VC] S. T. Vuong and J. A. Curgus, On Test Coverage Metrics for Communication Protocols, Proc. IWTCS, 1991.

- [YCL] N. Yevtushenko, A. Cavalli, L. Lima, *Test Suite Minimization for Testing in Context, Proc. IWTCS*, pp. 127-145, 1998.

- [ZV] J. Zhu and S. T. Vuong, Generalized Metric Based Test Selection and Coverage Measure for Communication Protocols, Proc. PSTV, pp. 299-314, 1997.

# Tool Demonstration Proposal: UML Validation Suite

Marc Lettrari<sup>1</sup> and Jochen Klose<sup>2</sup> and Udo Brockmeyer<sup>3</sup>

<sup>1</sup> OFFIS, Germany

<sup>2</sup> University of Oldenburg – Department of Computer Science

<sup>3</sup> OFFIS Systems and Consulting GmbH, Germany

e-mail:{marc.lettrari,jochen.klose}@informatik.uni-oldenburg.de

brockmeyer@o-s-c.de

# 1 Introduction

Distributed real-time computer systems are very complex and intrinsically difficult to specify and implement correctly. One cause is the lack of adequate methods and tools to deal with this complexity. The use of UML for developing such systems is gaining more and more attention both from research and industry.

A major goal in developing such systems is a validation that the design fulfills certain properties. Although there are some approaches with the goal of a formal proof of the correctness of a design [5, 4], testing still plays a dominant role. The reasons are the limited applicability of the methods which strive for a formal proof:

- Fully automatic methods (model checking) can only be applied to small designs and simple properties.

- Semi-automatic (with the help of theorem provers) or manual proofs are often very difficult and require significant knowledge and experience.

Conventional testing on the other hand is easier to do, but does not necessarily uncover all error situations. Therefore a fusion of the formal verification and testing approaches promises to improve the validation of software. Here we present a UVS (UML Validation Suite) tool for testing UML models designed with the Rhapsody tool of I-Logix, Inc. We add semantic rigor to the Rhapsody Sequence Diagrams (SDs) and use them to monitor or drive the interactive simulation of the UML model.

This proposal is organized as follows: We start with the formal foundation of Sequence Diagrams in section 2, followed by a quick overview of the features of the UVS tool and how it can be integrated into the design process in section 3. We conclude with information about the implementation of the tool in Sect. 4.

# 2 Sequence Diagrams

The Sequence Diagrams we are considering here are an enhanced version of the ones offered by the Rhapsody tool at the moment. In the context of monitoring and driving an UML design we need more expressiveness than that provided

by the UML standard. For this reason we have added a feature which we feel is essential for this application area: the capability to specify when a scenario described in a SD should be activated, i.e. when should we start to monitor the system or generate certain inputs? The simplest possibility would be to only consider *initial* SDs, i.e. those which are activated at system start. This is clearly too restrictive, since we also want to be able to use scenarios which are active more than once. We therefore introduce the concept of activation mode which can be either *initial* or *iterative*, where the second choice indicates that the SD can be activated several times, whenever the activation condition is true during a run of the system and the SD is not already active. For the iterative case another feature is needed, which allows us to specify when exactly the SD should be activated. Here we use an activation condition, a Boolean expression which characterizes the state of the Rhapsody design when the scenario should start. Both the activation mode and condition we have adopted from Live Sequence Charts (LSCs) [1] which are the formal base of the UVS tool.

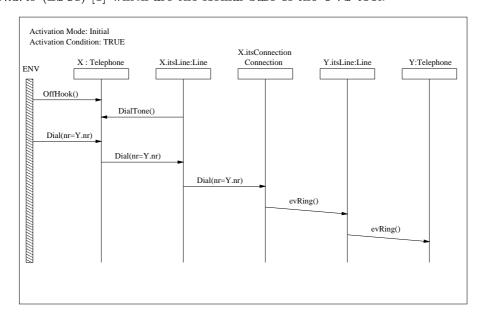

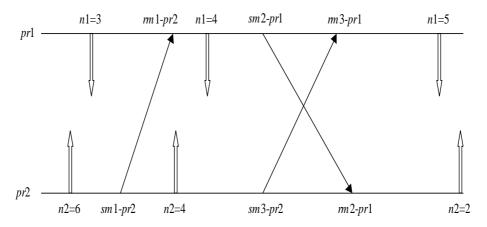

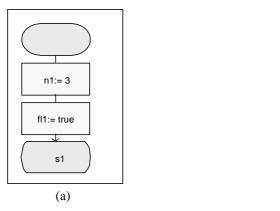

Fig. 1. Sequence diagram example SD1

Figure 1 shows an example SD, where a connection between two telephones is set up. The environment informs the telephone system that the receiver has been lifted off the hook, then the dial tone is heard in the receiver. Now the caller dials the telephone number of the callee which is propagated through the system. In the end the callee's phone rings.

The formal semantics for our SDs is given by an automaton which represents all the communication sequences allowed by the SD from which it is constructed. The algorithm for deriving this automaton from an SD is again taken from the LSC world (see [3] for a detailed description).

An error is indicated by the UVS tool when the order defined in the SD is violated by the simulation run, i.e. when an event or method call is observed at the wrong time. Consequently the only permissible order of the messages is the one shown in the SD. At this point also the activation of an SD comes into

play, since an error can only be detected when the corresponding SD has been activated.

# 3 Methodology

The typical UML development process (e.g. Rapid Object-oriented Process for Embedded Systems (ROPES) [2]) is iterative, starting with an early, fairly abstract version and progressing to more and more concrete prototypes. The first version will often be incomplete having some classes which are already well developed and others which are just empty shells, i.e. the classes exist together with their (incomplete) set of events and methods which are not implemented yet. An appropriate validation technique has to support such a development process which is often not the case.

Therefore we aim at an approach which supports validation throughout the whole development process. We use Sequence Diagrams as a graphical language to describe certain functional and real-time properties. We believe that Sequence Diagrams are well suited for such a testing process because of several reasons, e.g

- SDs are used early in the development process to capture the relevant use cases of the desired system. Therefore the testing process can run in parallel with the development process which allows early detection of functional or timing errors.

- The graphical fashion of SDs eases the communication between users, developers and test engineers. Therefore the acceptance of the developed systems will increase.

- Most of the common real-time properties (e.g. response times) can be expressed using SDs.

We show the application of our testing approach at 3 typical stages in the development process where we incrementally create early prototypes (testing during design), a first fully implemented design (unit testing) and an enhanced design (regression testing).

Suppose we have a system under construction where we want to test the already implemented classes. This is possible by designating the incomplete classes as stubs in the SD(s) and letting the test tool take over their behavior. The stubbed classes have to provide at least those interface objects (operations and event¹ receipts) which appear in the SD. The difference between monitoring and testing a SD is the way the environment is treated. If we want to monitor a SD, then we only observe if all described events and method calls occur in the right order and within the right time intervalls. If we want to test a SD, then the events coming from the environment (and the ones from stubbed instances) are generated automatically at the appropriate points in time, and all other messages are monitored.

<sup>&</sup>lt;sup>1</sup> Signals in UML terminology.

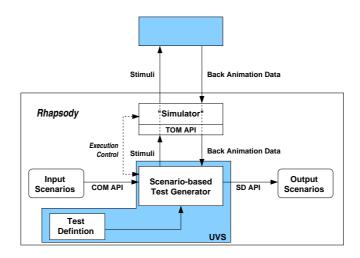

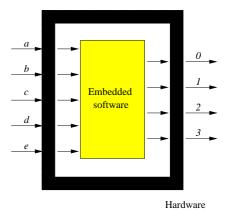

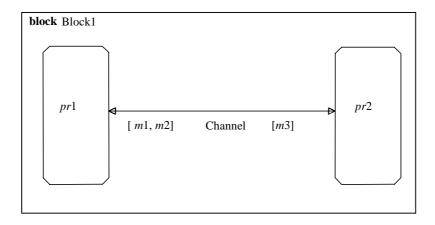

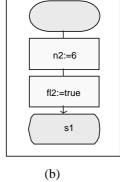

Fig. 2. Communication between UVS and Rhapsody

- In later iterations as the design becomes more and more complete the stubbed SD instances can be transformed into regular ones as the underlying classes become more complete. In general, SDs which have been specified in earlier iterations can be used for regression testing in the later phases, thereby becoming invariants of the model. Another important aspect of reusing SDs is the possibility to parameterize them. By using parameters such as "X" and "Y" as object names on SD instances all combinations of objects of the corresponding classes can be treated in one SD. If we want to use such an SD for monitoring or testing, we have to instantiate these parameters with concrete objects of the system.

- In each new iteration the existing SDs can be supplemented by new ones which specifically test those features which have been added in this iteration cycle. Of course, when inserting new functionality into a design, other functions should not be affected. To test this, we can use the SDs from the previous iterations for regression testing.

In our example we always used only one SDs at a time for testing, but our approach also allows complex tests consisting of several SDs whose activation can be controlled either implicitly by their activation mode and activation condition or explicitly by an ordering given by the user. Each test can consist of arbitrary many instances of SDs, which are SDs with instantiated parameters. This allows the definition of very complex tests where messages can be sent in parallel or sequentially to the application, whereas many monitors can observe the behaviour of the application.

# 4 Implementation

At present, the UVS tool is being integrated into Rhapsody and it will be part of the next release. In this section we briefly outline the software architecture of the UVS and its interaction with Rhapsody.

A prerequisite of our notion of testing is the possibility to interact with the system under test. For our approach it is important that the tester is informed

about every event and method call which is described in the considered SDs. Furthermore the tester must have the possibility to send events to the system under test. These capabilities can be realized in different ways (e.g. code instrumentation, model executor etc.). Figure 2 shows how UVS and Rhapsody interact with each other. The UVS manages the definition of the test cases and controls the test execution sending stimuli when required and observing the actions taken in the simulator.

We have integrated the whole test environment directly in Rhapsody. For each project the user can define arbitrarily many tests which are automatically stored together with the project files. For each test it can be specified which SDs it should contain, how the parameters should be instantiated and which SDs should run in parallel or sequentially. During the execution of the test the user is informed about which parts of the test behave as expected and which not. If an error was detected, a SD is generated automatically to visualize the error.

Rhapsody generates instrumented code, which communicates with a simulation interface (TOM API) during runtime. Whenever relevant things occur with regard to the considered SDs, the simulation interface informs the testing tool about them. Based on these notifications the testing tool detects possible errors or generates events automatically which can be send back to the implementation through the simulation interface.

#### References

- 1. W. Damm and D. Harel. LSCs: Breathing Life into Message Sequence Charts. In FMOODS'99 IFIP TC6/WG6.1 Third International Conference on Formal Methods for Open Object-Based Distributed Systems, 1999.

- 2. Bruce P. Douglass. Doing Hard Time. Addison-Wesley, 1999.

- Jochen Klose and Hartmut Wittke. An Automata Based Representation of Live Sequence Charts. In Tiziana Margaria and Wang Yi, editors, *Proceedings of TACAS 2001*, number 2031 in LNCS. Springer Verlag, 2001.

- 4. Diego Latella, Istvan Maijzik, and Mieke Massink. Towards a formal operational semantics of uml statechart diagrams. In 3rd International Conference on Formal Methods for Open Object-Oriented Distributed Systems, Lecture Notes in Computer Science. Kluwer Academic Publishers, 1999.

- 5. Johan Lilius and Ivan Porres Paltor. Formalising uml state machines for model checking. In R. France and B. Rumpe, editors, *UML'99 The Unified Modeling Language: Beyond the Standard*, number 1723 in Lecture Notes in Computer Science. Springer-Verlag, 1999.

# Automatic Test Generation from Statecharts Using Model Checking

# Hyoung Seok Hong, Insup Lee, Oleg Sokolsky

Department of Computer and Information Science University of Pennsylvania {hshong,lee,sokolsky}@saul.cis.upenn.edu

# Sung Deok Cha

Division of Computer Science and AITrc

Department of Electrical Engineering and Computer Science

Korea Advanced Institute of Science and Technology

cha@salmosa.kaist.ac.kr

#### Abstract

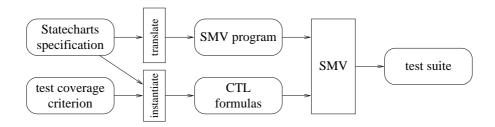

This paper discusses the application of model checking to test generation from specifications written in statecharts. We consider a family of coverage criteria based on the flow of control and data in statecharts and formulate the problem of test generation as finding counterexamples during the model checking of statecharts. The ability of model checkers to construct counterexamples allows test generation to be automatic

To illustrate our approach, we are based on the temporal logic CTL and its symbolic model checker SMV. We describe how to translate statecharts to inputs to SMV after defining the semantics of statecharts in terms of Kripke structures. We, then, describe how to express various coverage criteria in CTL and show how SMV can be used to generate only executable tests.

# 1 Introduction

This paper addresses the problem of test generation from statecharts [12] that have been widely used for specifying reactive systems. Statecharts can be regarded as extended finite state machines (EFSM) that support the hierarchical and concurrent structure on states and the communication mechanism through event broadcasting. Among several variants of statecharts considered in the literature [2], we concentrate on the STATEMATE semantics for statecharts [13]. Our approach, however, can be immediately applied to other variants of statecharts semantics, for example, the UML statecharts [24].

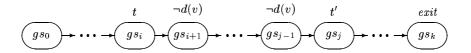

A statechart specification typically allows an infinite number of executions and hence exhaustive testing is impossible, which requires all the possible executions be performed. The prevalent testing practice is to construct a test suite, that is, a finite set of test sequences according to certain coverage criteria. For test coverage, we adapt the notions of control flow and data flow coverage used traditionally in software and protocol testing to statecharts. For test generation, we present an approach that involves the application of the temporal logic CTL [8] and its symbolic model checker SMV [21] to statecharts.

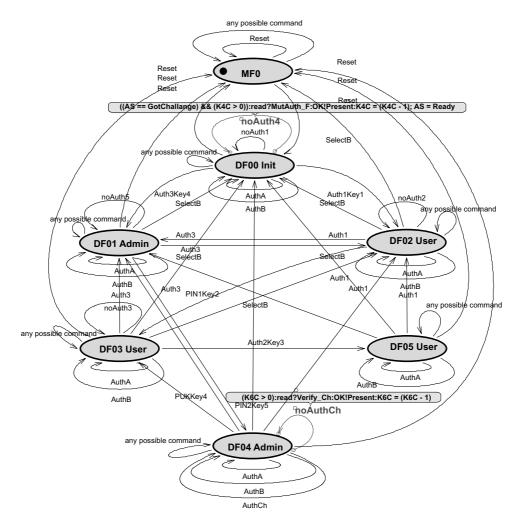

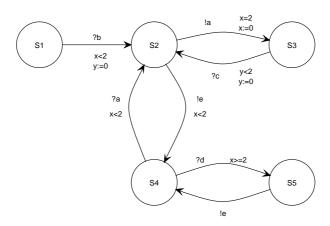

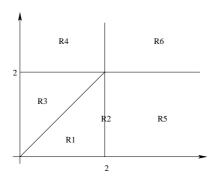

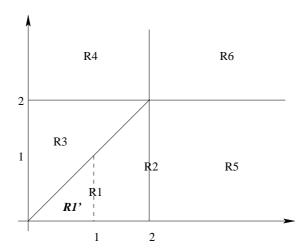

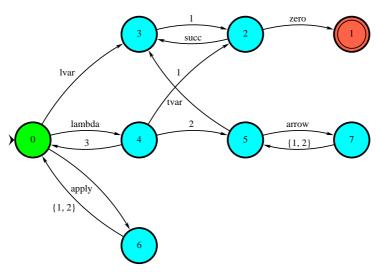

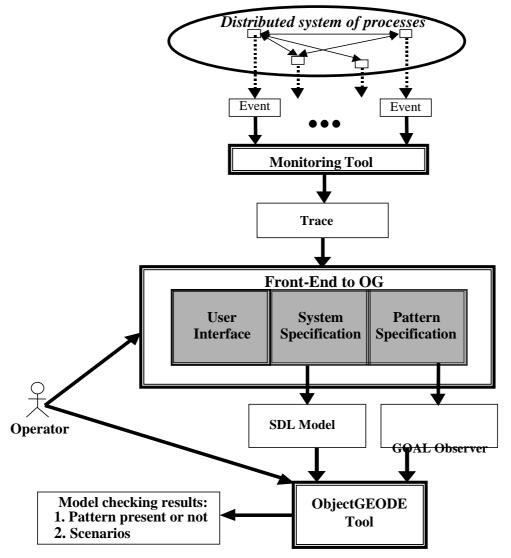

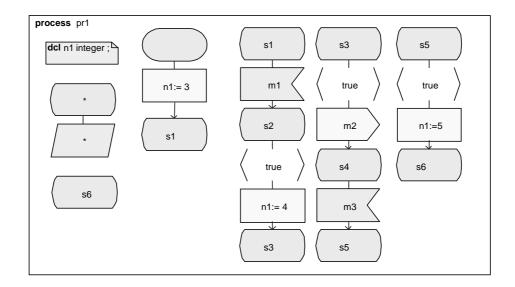

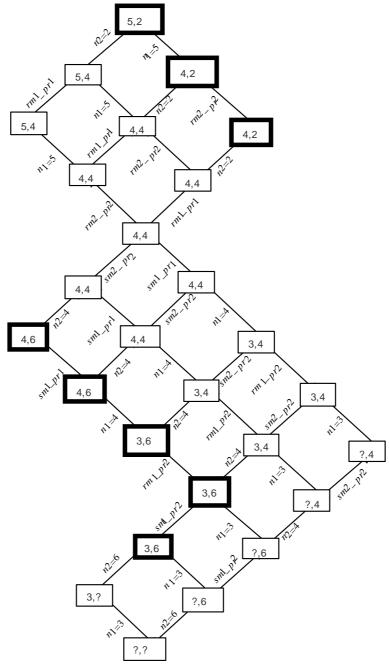

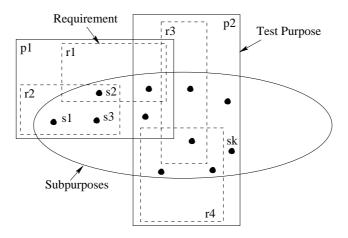

An overview of our approach is shown in Figure 1. The problem of test generation is formulated as a CTL model checking problem. A given coverage criterion is expressed as a parameterized collection of formulas in CTL that are instantiated for a given statecharts specification. Each formula describes a test sequence in abstract terms in such a way that the formula is true if and only if a statechart specification does *not* allow the test sequence. If the test sequence described by the formula can be performed by the specification, model checking will fail and the tool will generate a counterexample giving an execution sequence that explains why the formula cannot be satisfied. This counterexample is easily mapped into the test sequence by projecting it onto the observable events of the specification.

The contributions of this paper can be summarized as follows. We give a formal semantics for statecharts consistent with the STATEMATE informal interpretation. We apply a family of control-flow and data-

Figure 1: Overview of test generation

flow coverage criteria to state charts and give a CTL characterization of each coverage criterion. Finally, we demonstrate how to use SMV, an off-the-shelf CTL model checking tool, for the purpose of automatic generation of test suites from state charts.

Related work. Widely-used models for reactive systems in the testing literature include finite state machines (FSM), especially in hardware and protocol conformance testing. FSM-based testing methods primarily focus on the control-flow oriented test generation such as transition tour, unique-input-output sequence, distinguishing sequence, and characterizing sequence (see [3, 20] for survey). In protocol conformance testing, these methods have been extensively applied to formal description techniques [17] such as SDL and Estelle, and a number of automated tools have been developed (see [9] for survey).

EFSMs extend FSMs with variables to support the succint specification of data-dependent behaviors. If the state space of an EFSM is finite, one can obtain the equivalent FSM by unfolding the EFSM. Thus testing based on EFSMs with finite state space is reduced in principle to testing based on ordinary FSMs. This approach, however, suffers from the well-known state explosion problem which makes test generation often impractical. Even when test generation is feasible, this approach is often impractical because of the test explosion problem, i.e., the number of constructed tests might be too huge to be applied to implementations under test.

A promising alternative is to apply conventional software testing techniques to the generation of tests from EFSMs. In this approach, an EFSM is transformed into a flow graph that models the flow of both control and data of the EFSM and then tests are generated by identifying control and data flow information such as definitions and uses of variables in the flow graph [25]. The flow-graph test generation method is also applied to statecharts [15]. This approach abstracts from the values of variables and hence it can be applicable even if the state space is infinite. The approach, however, requires posterior analysis such as symbolic execution or constraint solving to determine the executability of tests and for the the selection of variable values which make tests executable.

The approach we advocate here is based on translating statecharts into Kripke structures and also suffers from the state explosion problem. However, the formulation of test generation as model checking in our approach enables the use of symbolic model checking [5], a technique that has been proven successful for controlling the state explosion problem. Second, our approach overcomes the test explosion problem by using the flow information of both control and data like the flow-graph approach. Finally, our approach can be seen as complementary to the flow-graph approach. On the one hand, flow graphs can be constructed for systems that are not finite-state. On the other hand, our approach has the advantage that only executable tests are produced.

Recently connections between test generation and model checking has been considered in the literature. A tool that uses test generation algorithms inspired by model checking algorithms is described in [18]. Test generation using counterexamples constructed by model checkers has been applied in several contexts. Mutation analysis is used in the approach of [1]. In [6], test generation is performed from user-specified temporal formulas, while in [10] testing purposes are used to generate tests. No consideration is given to coverage criteria. Some control-flow coverage criteria are considered in [11]. We are not aware of any work that considers the model checking approach to data-flow oriented test generation.

**Organization of the paper.** Section 2 reviews statecharts and CTL model checking. Section 3 gives a formal definition of the STATEMATE semantics. Section 4 introduces several notions relevant to specification-

based testing with statecharts. Section 5 and 6 describe a family of coverage criteria and a test generation method, respectively. Finally, Section 7 concludes the paper with a description of future work.

# 2 Preliminaries

This section provides a brief introduction to statecharts and CTL model checking.

#### 2.1 Statecharts

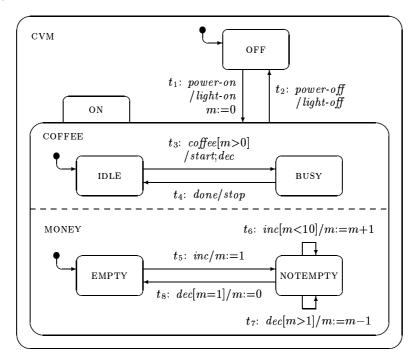

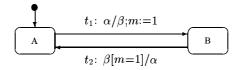

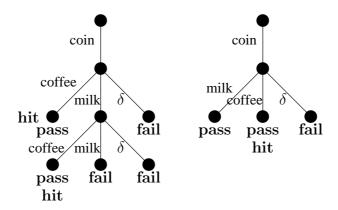

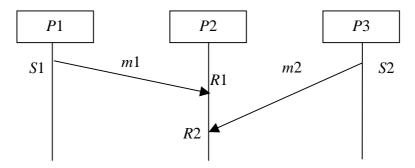

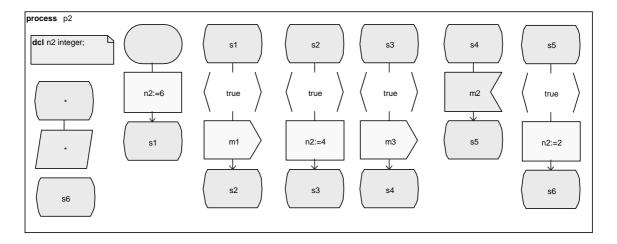

A statechart is a tuple  $Z=(S,\Pi,V,\Theta,T)$  where  $S,\Pi,V$ , and T are sets of states, events, variables, and transitions.  $\Theta$  is an interpretation of V which assigns to each variable its initial value. To demonstrate the main features of statecharts, we use as the running example the statechart shown in Figure 2, which specifies a simple coffee vending machine. The variable m in Figure 2 is of integer subrange [0,10] and its initial value is defined by  $\Theta(m)=0$ .

Figure 2: Example of Statecharts specification

One of the main features of statecharts is the hierarchical and concurrent structure on states. A state is either basic or composite. A composite state is classified as either OR-state or AND-state. An OR-state has substates related by exclusive-or-relation and has exactly one default substate. For example, the OR-state CVM in Figure 2 consists of OFF and ON with OFF as its default substate. Being in CVM implies being in OFF or in ON, but not in both. An AND-state has substates related by and-relation. Being in the AND-state ON implies being in COFFEE and MONEY at the same time. There is a unique state called the *root* at the highest level on the state hierarchy, say CVM.

For a state s, define children(s) as the set of substates of s and  $children^*$  as the reflexive-transitive closure of children. For two states  $s_1$  and  $s_2$ ,  $s_1$  is an ancestor of  $s_2$  if  $s_2 \in children^*(s_1)$ . If, in addition,  $s_1 \neq s_2$ , we say that  $s_1$  is a strict ancestor of  $s_2$ .

A configuration is a maximal set of states in which a system can be simultaneously. Precisely,  $C \subseteq S$  is called a configuration if (i) C contains the root state; (ii) for every AND-state s, either s and all substates of s are in C or they are all not in C; (iii) for every OR-state s, either s and exactly one substate of s are

in C or s and all substates of s are not in C. Each configuration can be uniquely characterized by its basic states. In Figure 2, we have the following configurations with  $\{OFF\}$  as the initial configuration:  $\{OFF\}$ ,  $\{IDLE, EMPTY\}$ ,  $\{IDLE, NOTEMPTY\}$ ,  $\{BUSY, EMPTY\}$ ,  $\{BUSY, NOTEMPTY\}$ .

We partition the set  $\Pi$  of events into three disjoint subsets  $\Pi_I$ ,  $\Pi_L$  and  $\Pi_O$  comprising input, local, and output events, respectively. The occurrence of input events is determined by the environment of a system while local and output events are generated by the system itself. Local events are used for internal communications and are assumed to be invisible to the environment. Input and output events are visible to the environment and constitute the observables of a statechart. In Figure 2, we have  $\Pi_I = \{power-on, power-off, coffee, done, inc\}$ ,  $\Pi_L = \{dec\}$ , and  $\Pi_O = \{light-on, light-off, start, stop\}$ .

A transition t is a tuple  $(source(t), trigger(t) \ guard(t), action(t), target(t))$  where  $source(t), target(t) \in S$ , trigger(t) is a predicate on  $\Pi$ , guard(t) is a predicate on V, action(t) consists of a set of assignments to V, denoted by assignments(t), and a set of events in  $\Pi_L \cup \Pi_O$ , denoted by generated(t).

For a transition t, define Exits(t) (resp. Enters(t)) as the set of states that a system exits (resp. enters) on taking transition t. For example, we have that  $Exits(t_1) = \{\text{OFF}\}$  and  $Enters(t_1) = \{\text{ON, COFFEE, IDLE, MONEY, EMPTY}\}$ . The formal definition for Exits(t) and Enters(t) can be found in [7]. The scope of a transition t, denoted by scope(t), is defined as the lowest OR-state in the state hierarchy that is a proper ancestor of both source(t) and target(t). For example,  $scope(t_2) = \text{CVM}$  and  $scope(t_3) = \text{COFFEE}$ . Two transitions t and t' conflict if scope(t) is an ancestor of scope(t')). For example,  $t_2$  and  $t_3$  conflict because CVM is an ancestor of COFFEE.

# 2.2 CTL Model Checking

Symbolic model checking [5] is a proven successful technique for the automatic verification of finite state systems. A widely-used temporal logic for symbolic model checking is the branching time temporal logic CTL [8]. Let AP be the underlying set of atomic propositions. The syntax for CTL is defined by the following grammar:

$$\phi ::= p \mid \neg \phi \mid \phi \land \phi' \mid EX\phi \mid AX\phi \mid E[\phi U\phi'] \mid A[\phi U\phi']$$

where  $p \in AP$  and  $\phi, \phi'$  range over CTL formulas. The remaining temporal operators are defined by the equivalence rules:  $EF\phi \equiv E[trueU\phi]; AF\phi \equiv A[trueU\phi]; EG\phi \equiv \neg AF(\neg \phi); AG\phi \equiv \neg EF(\neg \phi).$

The semantics of CTL is defined with respect to a Kripke structure  $M = (Q, Q_0, L, R)$  where Q is a finite set of states;  $Q_0 \subseteq Q$  is the set of initial states;  $L: Q \to 2^{AP}$  is the state-labeling function; and  $R \subseteq Q \times Q$  is the set of transitions. A sequence  $q_0, q_1, q_2, \ldots$  of states is a path if  $(q_i, q_{i+1}) \in R$  for all  $i \geq 0$ . A path  $\rho$  is a q-path if  $\rho(0) = q$ . The satisfaction relation  $\models$  is inductively defined as follows:

- $q \models p \text{ iff } p \in L(q); \ q \models \neg \phi \text{ iff } \neg (q \models \phi); \ q \models \phi \land \phi' \text{ iff } q \models \phi \text{ and } q \models \phi';$

- $q \models EX\phi$  (resp.  $AX\phi$ ) iff for some (resp. all) q-path  $\rho$ ,  $\rho(1) \models \phi$ ;

- $q \models E[\phi U \phi']$  (resp.  $A[\phi U \phi']$ ) iff for some (resp. all) q-path  $\rho$ , there exists  $i \ge 0$  such that  $\rho(i) \models \phi'$  and  $\rho(j) \models \phi$  for all  $0 \le j < i$ .

SMV [21] is a symbolic model checker for CTL which represents the state space and transition relation of Kripke structures using OBDDs [4]. An SMV program contains a set of variable declarations to determine its state space and descriptions of the initial states and transition relation, as well as a list of CTL formulas to be checked. Given a system model and a CTL formula, SMV automatically provides either a claim that the formula is satisfied in the system model or else a counterexample falsifying the formula.

Let V be a set of variables. We call v' as the primed version of a variable  $v \in V$  and use V' to denote the set of primed versions of all variables in V. We define a SMV program as a tuple (V, Init, Trans) where V is a finite set of variables; Init is a predicate on V; and Trans is a predicate on  $V \cup V'$ . Let  $\Sigma(V)$  be the set of all interpretations of V. A SMV program (V, Init, Trans) defines the Kripke structure  $(Q, Q_0, L, R)$  such that  $Q = \Sigma(V)$ ;  $Q_0 = \{\sigma \in \Sigma(V) \mid \sigma \models Init\}$ ;  $L(\sigma) = \{v = \sigma(v) \mid v \in V\}$ , for each  $\sigma \in \Sigma(V)$ ;  $(\sigma, \sigma') \in R$  if and only if  $\langle \sigma, \sigma' \rangle \models Trans$ , where  $\langle \sigma, \sigma' \rangle$  is the interpretation that assigns  $\sigma(v)$  to  $v \in V$  and  $\sigma'(v)$  to  $v' \in V'$ .

# 3 A Formal Definition of the STATEMATE Semantics

This section formally defines a statechart as a Kripke structure based on the STATEMATE semantics. We call each element in Q of a Kripke structure  $(Q, Q_0, L, R)$  a global state to distinguish it from a state of Statecharts. Similarly we call each element in R as a global transition. The formalization is used as the semantic foundation of the test coverage criteria and test generation method presented in the following sections.

The STATEMATE semantics uses the set of nonnegative integers N as the time domain and provides two models of time: synchronous and asynchronous. The main notion of the STATEMATE semantics is a step. A step represents the response of a system to the input events generated by the environment or the local events generated by the system itself. Both time models assume that the execution of a step takes zero time and differ in the way of how time is advanced relative to the execution of steps. In the former model, time is incremented by one time unit after the execution of each step. This time model is mainly used for highly synchronous systems such as synchronous circuits. In the latter, several steps are allowed to take place within a single point in time and time is incremented only when the system becomes stable. Intuitively, stability means that further steps are impossible without new input events. This paper focuses on the asynchronous time model.

**State space.** We give a set of rules that identify each component of a Kripke structure from a given statechart. First we represent the state space of a statechart  $Z = (S, \Pi, V, \Theta, T)$  using the following set of global states.

$$Q = Config \times \Sigma(V) \times 2^{\Pi} \times 2^{T \cup IT}$$

where Config is the set of all configurations of Z,  $\Sigma(V)$  is the set of all interpretations of V, and IT is the set of implicit transitions which shall be discussed in the next section. The set Q of global states captures the following information about a statechart: (i) the states in which a system is; (ii) the values of variables; (iii) the events generated; (iv) the transitions taken.

The set of initial global states is defined as follows:  $(C_0, \sigma_0, E_0, \tau_0) \in Q_0$  if  $C_0$  is the initial configuration,  $\sigma_0 = \Theta$ ,  $E_0 \in \Pi_I$ , and  $\tau_0 = \emptyset$ . This definition states that only input events can be generated and no transitions are taken prior to the system initialization.

The definition of the label of each global state  $(C, \sigma, E, \tau)$  is straightforward:

$$L((C, \sigma, E, \tau)) = in(C) \cup \{v = \sigma(v) \mid v \in V\} \cup E \cup \tau$$

where in(C) is a set of propositions defined as  $\{in(s) \mid s \in C\}$ .

**Transition relation.** In the asynchronous time model, input events can be introduced to a system only when the system becomes stable. Once input events are introduced, a sequence of steps is executed until the system becomes stable again. A global state  $(C, \sigma, E, \tau)$  is *stable* if there exists no generated input or local event, i.e.,  $E \cap (\Pi_I \cup \Pi_L) = \emptyset$ , and there exists no transition that may occur at that state.

We represent the transition relation of a statechart by the set of global transitions  $R = R_1 \cup R_2$ , where each global transition in  $R_1$  (resp.  $R_2$ ) is called *step* (resp. *tick*). A step transition starts from a non stable global state and manipulates configurations, variables and local and output events, while a tick transition starts from a stable global state and manipulates input events.

**Definition 3.1** Let  $(C, \sigma, E, \tau)$  and  $(C', \sigma', E', \tau')$  be global states.  $((C, \sigma, E, \tau), (C', \sigma', E', \tau'))$  is a *step transition* if and only if (1)  $(C, \sigma, E, \tau)$  is not stable; (2)  $C' = (C - \bigcup_{t \in \tau'} Exits(t)) \cup \bigcup_{t \in \tau'} Enters(t)$ ; (3)  $\sigma' = a(\sigma)$ , where  $a = \bigcup_{t \in \tau'} assignments(t)$ ; (4)  $E' = \bigcup_{t \in \tau'} generated(t)$ ; (5) each transition  $t \in \tau'$  is enabled at  $(C, \sigma)$ , i.e.,  $source(t) \in C$  and  $\sigma \models guard(t)$ , and is triggered by E, i.e., trigger(t) evaluates to true for E; no two transitions in  $\tau'$  conflict; and  $\tau'$  is maximal, i.e., each transition not in  $\tau'$  but triggered by E and enabled at  $(C, \sigma)$  conflicts with some transition in  $\tau'$ .

**Definition 3.2** Let  $(C, \sigma, E, \tau)$  and  $(C', \sigma', E', \tau')$  be global states.  $((C, \sigma, E, \tau), (C', \sigma', E', \tau'))$  is a *tick transition* if and only if  $(C, \sigma, E, \tau)$  is stable; C' = C;  $\sigma' = \sigma$ ;  $E' \subseteq \Pi_I$ ;  $\tau' = \emptyset$ .

Intuitively, a step transition  $((C, \sigma, E, \tau), (C', \sigma', E', \tau'))$  corresponds to the execution of the transitions in  $\tau'$ . A tick transition corresponds to the introduction of input events to a system.

**Nondeterminism.** A statechart Z is deterministic if each non-stable global state has only one successor. Note that stable global states may have more than one successor because tick transitions correspond to the introduction of input events. In this paper, we consider test generation only for deterministic Statecharts. Section 7 discusses a way to extend our approach to non-deterministic Statecharts.

In order to resolve certain classes of nondeterminism, the STATEMATE semantics provides a priority scheme based on the scope of transitions. Let t and t' be transitions conflicting each other. If scope(t) is a strict ancestor of scope(t'), then t has priority over t'. If scope(t) is equivalent to scope(t'), t and t' have the same priority. For example, in Figure 2  $t_2$  has priority over  $t_3$ ,  $t_4$ ,  $t_5$ ,  $t_6$ ,  $t_7$ , and  $t_8$ , while  $t_6$  and  $t_7$  have the same priority. With this priority scheme, the coffee vending machines becomes deterministic with respect to  $\langle \{power-on\}, \{inc\}, \{power-off, coffee\} \rangle$  because now we have  $\langle \{light-on\}, \emptyset, \{light-off\} \rangle$  as the only possible output sequence.

# 4 Specification-Based Testing with Statecharts

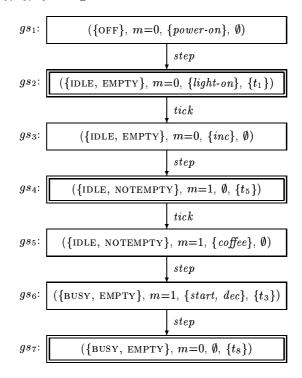

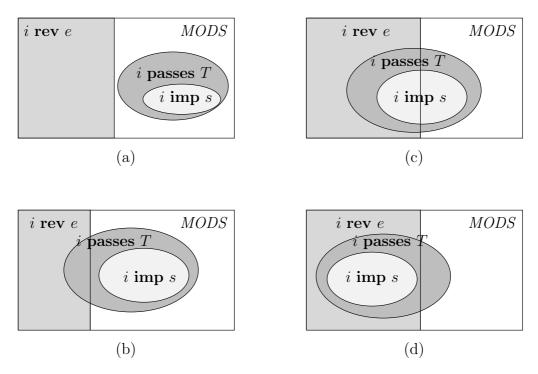

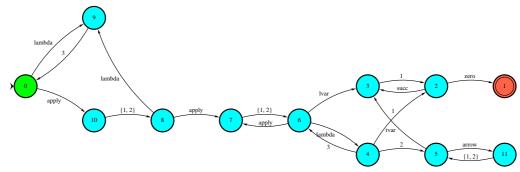

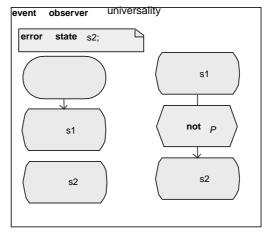

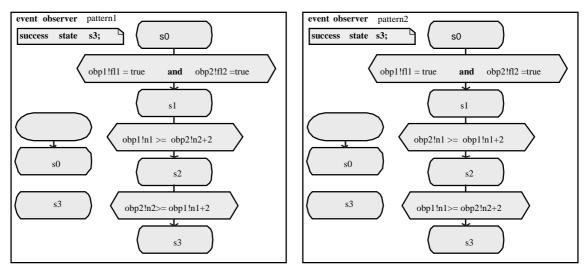

Runs. Let  $Z = (S, \Pi, V, \Theta, T)$  be a statechart. A naive approach to characterizing the behavior of a statechart is to use all the finite paths of its Kripke structure M(Z). This approach, however, is of little use because a path ending at a non stable global state may not provide the information of the output sequence that is supposed to be generated as the response to an input sequence. Therefore we are concerned about only finite paths ending at a stable global state, which we call runs. Figure 3 shows a run of the coffee vending machine in which double rectangles represent stable global states. The run corresponds to the execution of the transition sequence  $t_1$ ,  $t_5$ ,  $t_3$ ,  $t_8$  in Figure 2.

Figure 3: A run for test sequence  $\{power-on\}, \{inc\}, \{coffee\}/\{light-on\}, \emptyset, \{start\}\}$

A subsequence  $(C_i, \sigma_i, E_i, \tau_i)$ , ...,  $(C_j, \sigma_j, E_j, \tau_j)$  of a run  $(C_0, \sigma_0, E_0, \tau_0)$ , ...,  $(C_n, \sigma_n, E_n, \tau_n)$  is a superstep if  $(C_{i-1}, \sigma_{i-1}, E_{i-1}, \tau_{i-1})$  is stable,  $(C_k, \sigma_k, E_k, \tau_k)$  is not stable for  $i \leq k < j$ , and  $(C_j, \sigma_j, E_j, \tau_j)$  is stable.

We refer to  $E_i$  as the input of the superstep and  $\Pi_O \cap \bigcup_{i < k \leq j} E_k$  as the output of the superstep. For example, the following shows the three supersteps in Figure 3.

| superstep        | input                 | output           |

|------------------|-----------------------|------------------|

| $gs_1,\ gs_2$    | $\{power-on\}$        | $\{light - on\}$ |

| $gs_3,\ gs_4$    | $\{inc\}$             | Ø                |

| $gs_5,gs_6,gs_7$ | $\{\mathit{coffee}\}$ | $\{start\}$      |

Test sequences. We refer to a finite word  $\bar{i}=i_1...i_n$  over  $2^{\Pi_I}$  as input sequence and a finite word  $\bar{o}=o_1...o_n$  over  $2^{\Pi_O}$  as output sequence. We say that a pair of input and output sequences, written as  $\bar{i}/\bar{o}$ , is a test sequence if there is a run such that  $i_j$  and  $o_j$  are the input and output of the j-th superstep of the run, respectively. Note that since we consider only deterministic statecharts, there is only one output sequence corresponding to each input sequence. Intuitively a test sequence  $\bar{i}/\bar{o}$  describes the expected or required response  $\bar{o}$  of implementations under test to the input sequence  $\bar{i}$ . We say that a test suite is a set of test sequences. For example, we have the test sequence  $\{power-on\}, \{inc\}, \{coffee\}/\{light-on\}, \emptyset, \{start\}\}$  from the run in Figure 3.

Exit nodes. We compare the nature of test sequences for reactive systems with those for transformational systems. Most of analysis and testing models for transformational systems, e.g., flow graphs[14] and program dependency graphs[19], contain a distinguished node called exit node to model the terminating behavior of such systems. Test sequences in such graphs are naturally defined in terms of paths whose first node is the entry node and last node is the exit node of the graphs. On the other hand, there is no corresponding notion in reactive system models, because the behavior of reactive systems is characterized by their non-terminating computations.

When defining test sequences for statecharts, we do not put any constraint on input sequences and thus allow the execution of test sequences may end at any stable global state. That is, we regard each stable global state as a pseudo-exit node. There are, however, more elaborate approaches to defining exit nodes. A widely used approach in EFSM-based testing is to require that the execution of test sequences end at an initial state from which another test sequence can be applied. In general, testers may want to designate an arbitrary state as an exit node. An interesting notion is marker state in the supervisory control theory by Ramadge and Wonham[22]. This theory distinguishes the paths ending at a state designated as a marker from others and interprets such paths as completed tasks of the modeled system. For example, a tester may want to designate the configuration {IDLE, EMPTY} as a marker for the coffee vending machine and require that the execution of every test sequence end at the marker. In this case, the input sequences in Figure 3 and can be extended with {done} to guarantee that the machine end at the marker.

Testing quiescence. Often we need to test that the system does not produce any output in response to some input. For example, the coffee vending machine in configuration {IDLE, EMPTY} when m=0 does not respond to input {coffee} simply because there are no enabled transitions in the corresponding global state. However, if we want to generate a test for such quiescent behavior using the same technique as for observable behaviors, we need to make the absence of output explicit. For this, we extend the set of transitions of the statechart with  $implicit\ transitions$ . Implicit transitions are always self-loops with the empty set of output events. The following shows the implicit transitions for the coffee vending machine.

```

\begin{array}{l} it_1 = it(\text{Off},power\text{-}of\!f) = (\text{Off},\ power\text{-}of\!f,\ true},\ \emptyset,\ \text{Off}) \\ it_2 = it(\text{Off},cof\!f\!e\!e}) = (\text{Off},\ cof\!f\!e\!e},\ true,\ \emptyset,\ \text{Off}) \\ it_3 = it(\text{Off},done) = (\text{Off},\ done,\ true},\ \emptyset,\ \text{Off}) \\ it_4 = it(\text{Off},inc) = (\text{Off},\ inc,\ true},\ \emptyset,\ \text{Off}) \\ it_5 = it(\text{Off},dec) = (\text{Off},\ dec,\ true},\ \emptyset,\ \text{Off}) \\ it_6 = it(\text{On},power\text{-}on) = (\text{On},\ power\text{-}on,\ true},\ \emptyset,\ \text{On}) \\ it_7 = it(\text{IDLe},cof\!f\!e\!e}) = (\text{IDLe},\ cof\!f\!e\!e},\ \neg(m>0),\ \emptyset,\ \text{IDLe}) \\ it_8 = it(\text{BUSY},cof\!f\!e\!e}) = (\text{BUSY},\ cof\!f\!e\!e},\ true,\ \emptyset,\ \text{BUSY}) \\ it_9 = it(\text{IDLe},\ done) = (\text{IDLe},\ done,\ true},\ \emptyset,\ \text{IDLe}) \end{array}

```

```

it_{10} = it(\text{NOTEMPTY}, inc) = (\text{NOTEMPTY}, inc, \neg (m < 10), \emptyset, \text{NONEMPTY})

it_{11} = it(\text{EMPTY}, dec) = (\text{EMPTY}, dec, true, \emptyset, \text{EMPTY})

it_{12} = it(\text{NOTEMPTY}, dec) = (\text{NOTEMPTY}, dec, \neg (m > 1 \lor m = 1), \emptyset, \text{NONEMPTY})

```

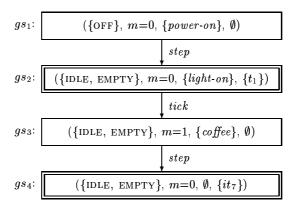

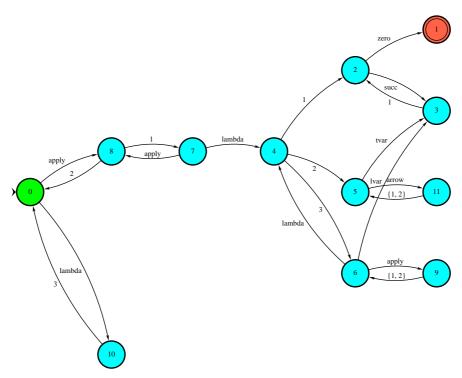

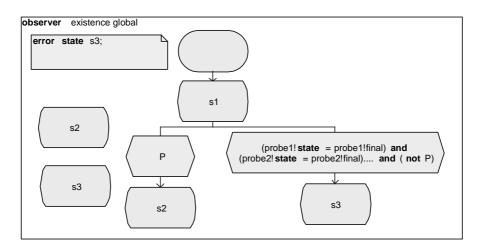

An input sequence  $\bar{i}$  is explicit if there exists a test sequence  $\bar{i}/\bar{o}$  such that each step transition of its run corresponds to the execution of an explicit transition. Otherwise, it is *implicit*. For example, the input sequence  $\langle \{power-on\}, \{inc\}, \{coffee\} \rangle$  is explicit (see Figure 3), while  $\langle \{power-on\}, \{coffee\} \rangle$  is implicit because the step transition  $(gs_3, gs_4)$  in Figure 4 corresponds to the execution of  $it_7$ .

Figure 4: A run for test sequence {power-on},{coffee}/{light-on},∅

**Conformance.** Finally we present a conformance relation between specifications written in deterministic statecharts and implementations under test. For a statechart Z and implementation I, we write  $Z\langle \bar{i} \rangle$  and  $I\langle \bar{i} \rangle$  for the output sequences of Z and I to an input sequence  $\bar{i}$ , respectively. We say that I weakly conforms to Z if  $Z\langle \bar{i} \rangle = I\langle \bar{i} \rangle$ , for all explicit input sequences  $\bar{i}$ . We say that I strongly conforms to Z if  $Z\langle \bar{i} \rangle = I\langle \bar{i} \rangle$ , for all input sequences  $\bar{i}$ .

# 5 Test Coverage Criteria for Statecharts

Statecharts specify the required behavior of implementations under test by describing the possible sequences of input and output events in terms of control and data dependencies between the events. Specification-based testing with statecharts aims at determining whether an implementation establishes the desired flow of both control and data expressed in its specification.

# 5.1 Control Flow Oriented Coverage Criteria

Obviously the strongest test coverage criteria is *path coverage* which requires that all the runs of a statechart be traversed, or equivalently all the input sequences of the statechart be applied to implementations under test. Because there is an infinite number of input sequences, we need to have systematic coverage criteria that select a finite and reasonable number of test sequences satisfying certain conditions. This paper presents a family of test coverage criteria based on the flow information of both control and data in statecharts.

We say that a test sequence  $\bar{i}/\bar{o}$  covers a state s (resp. configuration C and transition t) if its run contains global state  $(C_i, \sigma_i, E_i, \tau_i)$  such that  $s \in C_i$  (resp.  $C = C_i$  and  $t \in \tau$ ).

**State coverage.** A test suite P satisfies state coverage if each state is covered by a test sequence in P.

Configuration coverage. A stronger criterion than state coverage may be defined which requires the traversal of each configuration. A test suite P satisfies configuration coverage if each configuration is covered by a test sequence in P.

**Transition coverage.** A test suite P satisfies weak transition coverage if each explicit transition is covered by a test sequence in P. A test suite P satisfies strong transition coverage if each explicit and implicit transition is covered by a test sequence in P.

# 5.2 Data Flow Oriented Coverage Criteria

We adopt the following convention which classifies each variable occurrence of a transition as being a definition, computation use (c-use), and predicate use (p-use). Let v be a variable and t be a transition. v is defined at t if assignments(t) includes an assignment that defines v; v is c-used at t if assignments(t) includes an assignment that references v; v is p-used at t if guard(t) references v. We denote by def(v), c-use(v), and v-use(v) the sets of transitions that define, v-use, and v-use(v). In the coffee vending machine, we have  $def(v) = \{t_1, t_5, t_6, t_7, t_8\}$ , v-use(v) =  $\{t_6, t_7\}$ , v-use(v) =  $\{t_8, t_6, t_7, t_8\}$ .

Let t and t' be transitions and  $gs_0, \ldots, gs_n$  be a run. Suppose that the step transitions  $(gs_i, gs_{i+1})$  and  $(gs_j, gs_{j+1})$  such that  $0 \le i < j < n$  correspond to the execution of t and t', respectively. The run is a definition-clear run with respect to v from t to t' if each step transition  $(gs_k, gs_{k+1})$  does not correspond to the execution of any transition at which v is defined, for i < k < j.

We define associations between definitions and uses of a variable as follows: a tuple (v,t,t') is a def-c-use association (resp. def-p-use association) if  $t \in def(v)$ ,  $t' \in c$ -use(v) (resp.  $t' \in p$ -use(v)), and there exists a definition-clear run with respect to v from t to t'. A def-use association is either a def-c-use association or def-p-use association. Table 1 shows the def-use associations for the coffee vending machine. For example, consider the def-p-use association  $(m, t_5, t_3)$ . The definition of m at  $t_5$  can reach the use of m at  $t_3$  through the definition-clear run shown in Figure 3. In general, there are three types of associations between definitions and uses in statecharts. The first type includes associations which occur within an OR-state, e.g.,  $(m, t_5, t_6)$ . Associations occurring in ordinary EFSMs belong to this type. The second type is caused by the hierarchical structure on states, e.g.,  $(m, t_1, it_7)$ . The third type is caused by the concurrent structure on states, e.g.,  $(m, t_5, t_3)$ .

Table 1: The def-use associations for the coffee vending machine

| def-c-use associations         | def-p-use associations                                       |

|--------------------------------|--------------------------------------------------------------|

| $(m,t_5,t_6)$                  | $(m, t_5, t_3), (m, t_5, t_6), (m, t_5, t_8)$                |

| $(m, t_6, t_6), (m, t_6, t_7)$ |                                                              |

| $(m, t_7, t_6), (m, t_7, t_7)$ | $(m, t_7, t_3), (m, t_7, t_6), (m, t_7, t_7), (m, t_7, t_8)$ |

We also account for the data flow caused by implicit transitions. A def-use association for a variable v is called *implicit* if v is referenced by the guard of an implicit transition. Note that only p-uses are possible for implicit transitions. In the coffee vending machine, we have the following implicit def-p-use associations:  $(m, t_1, it_7), (m, t_6, it_{10}), (m, t_8, it_7)$ .

We say that a test sequence  $\bar{i}/\bar{o}$  covers a def-use association (v, t, t') if its run is a definition-clear run with respect to v from t and t'.

**All-def coverage.** A test suite P satisfies weak all-def coverage if for each variable v and each transition t such that  $t \in def(v)$ , some def-use association (v,t,t') is covered by a test sequence in P. A test suite P satisfies strong all-def coverage if for each variable v and each transition t such that  $t \in def(v)$ , some explicit def-use association (v,t,t') or implicit def-use association (v,t,it) is covered by a test sequence in P.

**All-use coverage.** A test suite P satisfies weak all-use coverage if for each variable v and each transition t such that  $t \in def(v)$ , each def-use association (v, t, t') is covered by a test sequence in P. A test suite P

satisfies strong all-use coverage if for each variable v and each transition t such that  $t \in def(v)$ , each explicit def-use association (v, t, t') and implicit def-use association (v, t, it) is covered by a test sequence in P.

# 6 A Test Generation Method for Statecharts

This section shows that test generation from statecharts can be automatically performed by using the SMV's ability to construct counterexamples. Briefly the generation of a test suite from a statechart and a test coverage criterion consists of the following steps.

- An SMV program is constructed from the statechart.

- A set of CTL formulas is constructed from the criterion.

- A test suite is constructed by model-checking the CTL formulas against the SMV program and projecting the obtained counterexamples onto the observable events.

# 6.1 Statecharts as SMV Programs